### UNIVESIDAD NACIONAL DE INGENIERÍA

Facultad de ingeniería Electricidad y Electrónica

# Diseño de un Sistema de Entrada de Datos a Base de Microprocesador

TESIS

PARA OPTAR EL TITULO PROFESIONAL DE

INGENIERO ELECTRONICO

Félix Augusto Valladares Pérez

Promoción 1982-2

Lima - Perú 1985

"Al amor y sacrificio de dos mujeres ejemplares: mi madre , mi novia".

UNIVERSIDAD NACIONAL DE INGENIERIA Facultad de Ingeniería Electrónica

"Diseño de un Sistema de Entrada de Datos a Base de Microprocesador"

Autor: Félix Augusto Valladares Pérez

Proyecto para optar el Título de Ingeniero Electrónico

Lima - 1985

#### **EXTRACTO**

El objetivo es el diseño de un sistema que permita el almacenamiento masivo de información en forma ordenada y capaz de ser posteriormente procesada por un computador.

El medio de entrada de datos son las estaciones ter minales, las cuales constan de 1 teclado y una pantalla en la cual se observan los datos que estan siendo introducidos. El sistema diseñado es capaz de trabajar a la vez con 8 de estas estaciones terminales conectadas en una configuración de cadena.

El almacenamiento de los datos que vienen de las es taciones terminales se efectúa temporalmente en un disco magnético en el que se clasifica la información, según el tipo de trabajo de digitación, siguiendo los pasos da

dos por un Sistema Operativo.

Los datos almacenados en el disco son posteriormente grabados en una cinta magnética, la cual como medio de almacenamiento final y a través de la cual se le entregará al computador los datos para que éste efectúe el cómputo respectivo.

El trabajo efectuado fue básicamente el diseño de la Unidad de Control que dirija todas las operaciones del sistema, de las respectivas interfaces con las unidades de disco y cinta magnética y la recepción de los datos que provienen de todas las estaciones terminales.

Esta Unidad de Control está centralizada en el Microprocesador Z-80. El Z-80 comanda todas las operaciones ejecutando el Sistema Operativo residente en una memoria EPROM. El Z-80 posee también memoria RAM de trabajo, en la cual almacena todos los datos que se dirigen a la Cinta o Disco.

La generación del video se efectúa con el Controlador de Video 5027 y una memoria RAM. El 5027 provee las señales de sincronismo que van hacia la pantalla y direcciona a la memoria RAM que contiene los caracteres que van a displayarse.

La Unidad de Control también comprende las interfases. La Interface con la cinta consiste básicamente de la Interface Paralela Programable 8255, mientras que la Interface con el disco es b\(\frac{1}{2}\)icamente una l\(\frac{1}{2}\)jorda de acceso directo a memoria (D.M.A.).

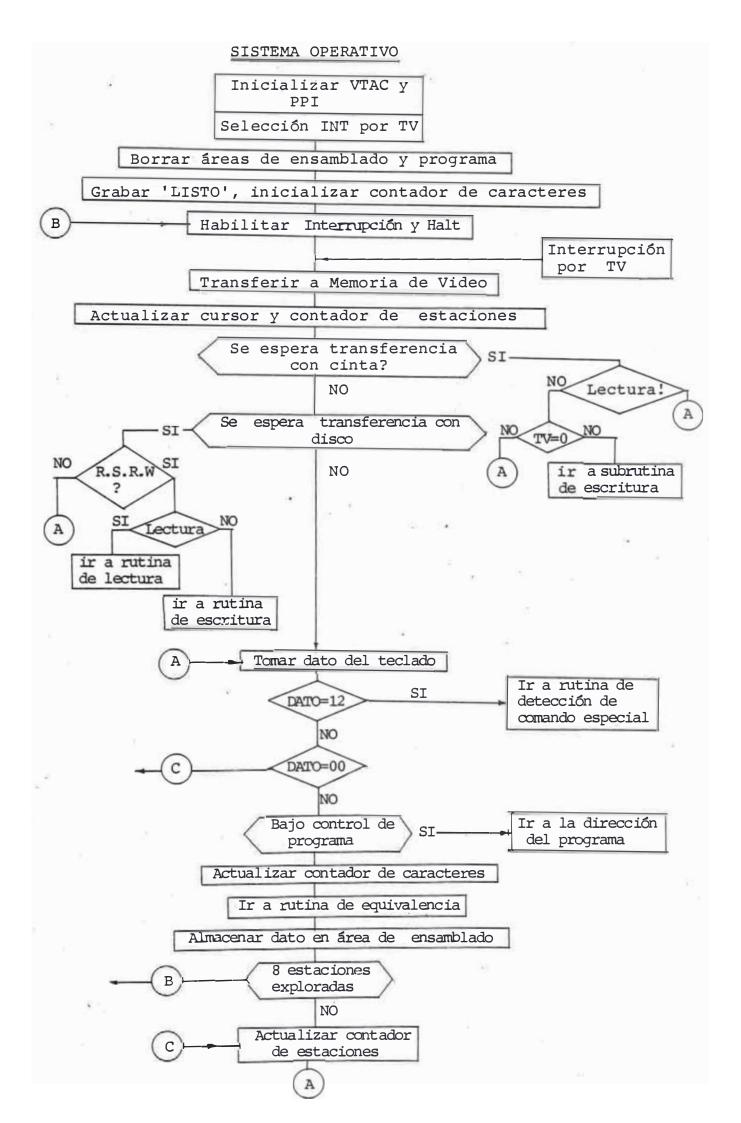

La Interface con las Estaciones Terminales es a tra vés de registros de 3 estados, el 280 se encuentra contí nuamente haciendo el rastreo de las estaciones, una por vez, para tomar los datos que se encuentran almacenados en sus registros. Estos datos son colocados en la memoria RAM en zonas definidas para cada estación, llamadas Areas de Ensamblado. El Sistema Operativo en todo momen to pregunta si alguna estación ha hecho alguna requisi - ción de transferencia con el disco o la cinta para efectuar las rutinas correspondientes.

De esta forma, todas las estaciones son capaces de realizar las mismas funciones.

Opcionalmente, el Sistema fue dotado de un Controla dor de Comunicaciones (USART), teniendo así la posibilidad de comunicarse por vía telefónica con un Computador Remoto para transmitir los datos que se encuentran grabados en la cinta o en el disco. El USART usado es el 8251, cuyo funcionamiento es completamente programable por el 280. El modo de transmisión elegido es el de una comunicación Síncrona con 2 bytes de sincronismo (Bi-síncrona) y ajustándose al protocolo de comunicación B.S.C. (comunicación Binaria Síncrona).

Los programas de prueba y el sistema operativo han sido escritos en lenguaje Assembler y acompañados del có

digo binario para mayor claridad de los lectores y los listados se encuentran en los apéndices respectivos. Así mismo, los diagramas de flujo correspondientes a estos programas se encuentran en el capítulo que trata la Programación del Sistema.

Todo el diseño circuital se llevó a la práctica mediante la construcción de un prototipo, en el cual se mon taron todos los componentes.

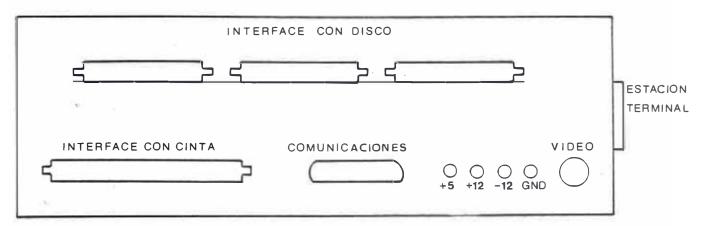

El Prototipo implementado consiste de placas de cir cuito impreso de propósitos generales con el cableado efectuado en el lado de los componentes. Todo el conjunto se encuentra dispuesto en un armazón metálico donde se encuentran también los conectores para interactuar con la Unidad de Disco, Unidad de Cinta, Estaciones Terminales, Modem externo y las fuentes de alimentación.

Todo el sistema trabaja con fuentes de +5, +12 y -12 voltios.

### TABLA DE CONTENIDO

|      |                                          | Pág |

|------|------------------------------------------|-----|

| PROI | uogo                                     | 1   |

| CAPI | TULO I: INTRODUCCION                     | 4   |

| 1.1  | Consideraciones Preliminares             | 4   |

| 1.2  | Descripción de un Sistema Independiente  |     |

|      | de Entrada de Datos                      | 8   |

| 1.3  | El Sistema Inteligente de Entrada de     |     |

|      | Datos de Inforex                         | 10  |

| 1.4  | Descripción básica del Sistema Diseñado  | 14  |

| CAPI | TULO II: LA UNIDAD CENTRAL DEL SISTEMA   | 21  |

| 2.1  | Fundamentos de la Unidad Central         | 21  |

| 2.2  | Direccionamiento y Decodificación del    |     |

|      | Sistema                                  | 23  |

| 2.3  | Lógica de Interrupciones                 | 24  |

| 2.4  | Sistema de Video                         | 27  |

| CAPI | TULO III: DESCRIPCION DE LA UNIDAD DE    |     |

|      | DISCO                                    | 32  |

| 3.1  | La Unidad de Disco marca Diablo Modelo   |     |

|      | 44-8                                     | 32  |

| 3.2  | Señales de Control de la Unidad de Disco |     |

|      | Diablo                                   | 38  |

| 3.3  | Operaciones Típicas con la Unidad de Dis |     |

|      | co Diablo                                | 4   |

### - VIII -

|      |                                            | Pấg |

|------|--------------------------------------------|-----|

| 3.4  | Descripción de la Interface con la Uni-    |     |

|      | dad de Disco Diablo                        | 50  |

| CAPI | TULO IV: DESCRIPCION DE LA UNIDAD DE CINTA | 57  |

| 4.1  | Características de la Unidad de Cinta      |     |

|      | marca Inforex                              | 57  |

| 4.2  | Interface con la Unidad de Cinta           | 64  |

| 4.3  | Bytes de Chequeo, LRCC y CRCC              | 73  |

| 4.4  | Generación del Polinomio de CRCC           | 76  |

| CAPI | TULO V: DESCRIPCION DE LOS ORGANOS TERMI-  |     |

|      | NALES DE ENTRADA DE DATOS                  | 82  |

| 5.1  | Fundamentos del Diseño de los Terminales   |     |

|      | de Entrada de Datos                        | 82  |

| 5.2  | Programación del Controlador de Video      |     |

|      | VTAC-5027                                  | 88  |

| 5.3  | Decodificación de la Señal de Blanking     | 94  |

| CAPI | TULO VI: OPCION DE COMUNICACIONES          | 97  |

| 6.1  | Introducción                               | 97  |

| 6.2  | La Interface serial USART 8251             | 98  |

| 6.3  | Programación del USART 8251                | 100 |

| 6.4  | El Modem MC-14412                          | 103 |

| 6.5  | Descripción del Hardware de la Opción de   |     |

|      | Comunicaciones                             | 108 |

| 6.6  | Las recomendaciones del C.C.I.T.T., E.I.A. | 114 |

| 6.7  | Protocolo de Comunicación B.S.C.           | 117 |

|                                              | Pág. |

|----------------------------------------------|------|

| CAPITULO VII: PROGRAMACION DEL SISTEMA       | 124  |

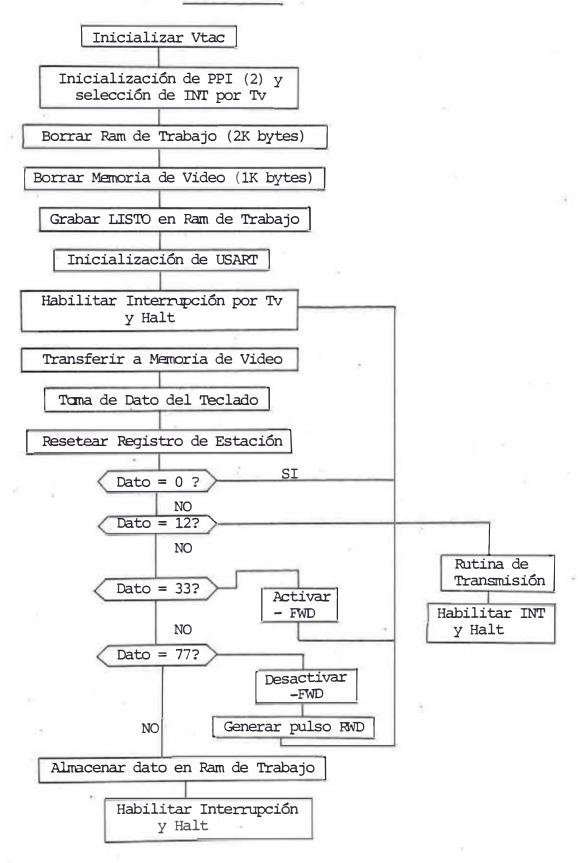

| 7.1 Programa de Diagnóstico                  | 124  |

| 7.2 Programa resumido de Prueba N°1          | 127  |

| 7.3 Programa resumido de Prueba N°2          | 133  |

| 7.4 Sistema Operativo                        | 138  |

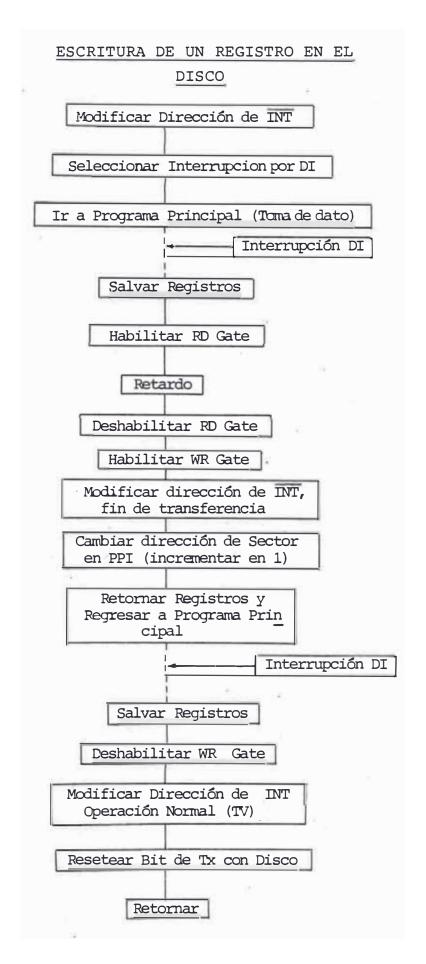

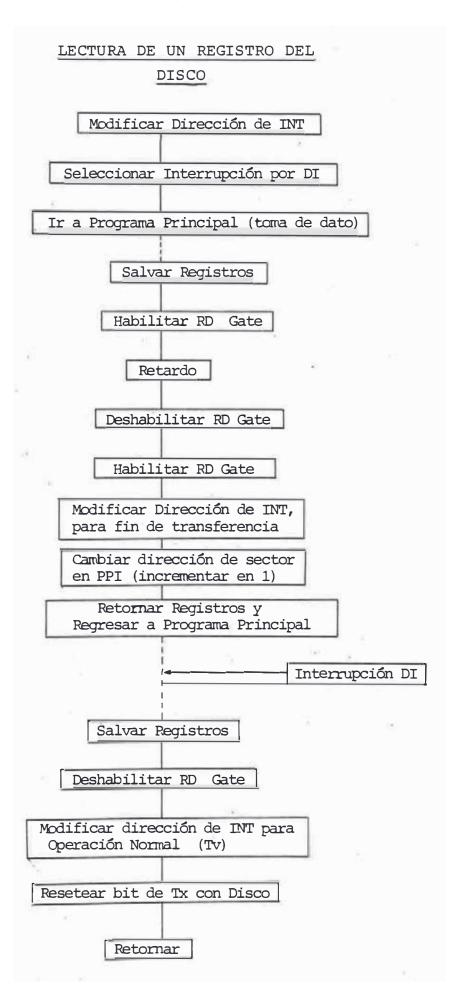

| 7.5 Asignación de Trabajo en el Disco        | 154  |

| 7.6 Los Comandos Especiales                  | 157  |

| CAPITULO VIII: RESULTADOS EXPERIMENTALES     | 172  |

| CONCLUSIONES                                 | 185  |

| BIBLIOGRAFIA                                 | 192  |

| APENDICE 1: DESCRIPCION BASICA DE UNA UNIDAD |      |

| DE DISCO                                     | 193  |

| APENDICE 2: DESCRIPCION BASICA DE UNA UNIDAD |      |

| DE CINTA                                     | 198  |

| APENDICE 3: PROGRAMA DE DIAGNOSTICO          | 204  |

| APENDICE 4: PROGRAMA DE PRUEBA Nº1           | 207  |

| APENDICE 5: PROGRAMA DE PRUEBA N°2           | 212  |

| APENDICE 6: LISTADO DEL SISTEMA OPERATIVO    | 220  |

| APENDICE 7: DIAGRAMA CIRCUITAL DEL SISTEMA   | 241  |

\*\*\*

#### **PROLOGO**

El presente trabajo contempla el diseño de un Siste ma de Entrada de Datos, el establecimiento de todos los criterios necesarios para hacerlo competitivo con los sis temas actualmente existentes en nuestro medio y, asimismo, la construcción de un prototipo con el cual se demuestra que los resultados del diseño preliminar pueden ser llevados a la práctica. Es importante, sin embargo, advertir que no todos estos resultados han sido probados experimentalmente, debido a la practicamente inacabable cantidad de opciones y mejoras que se pueden hacer al presente sistema, sobre todo en lo que concierne al Sistema Operativo.

Cabe resaltar que el presente trabajo es fundamental mente práctico, tecnológico, debido a los objetivos plan teados al inicio del mismo: diseñar un Sistema de Entrada de Datos basado en los sistemas ya existentes pero con criterios propios y auténticos, usando infraestructu ra disponible en nuestro medio, un sistema capaz de ser construido y presentado al público. Lamentablemente, no se ha desarrollado ningún estudio teórico, fundamental mente porque no era necesario, pero si se ha tenido todo momento en mente algunos importantes criterios teóricos

aprendidos en la Universidad a lo largo del Diseño Cir - cuital del Sistema.

En el desarrollo de este informe se ha omitido explicaciones respecto a los principios básicos de funciona - miento del Microprocesador y de algunos de sus periféricos debido a que este se ha hecho muy popular y ha sido escrita abundante literatura sobre su operación. Con respecto a las Unidades de Cinta y Disco, cuyo conocimien to no está aún muy difundido en nuestro medio, se incluye un apéndice con sus principios básicos de operación. En el Apéndice se incluyen también los listados de todos los programas que han sido usados para probar el funcionamiento del Sistema.

En todo momento se ha procurado ser lo más claro po sible en la explicación de los conceptos y razones del diseño para que sean de utilidad a futuros trabajos que se realicen en este campo. También quisiera manifestar que el uso de gran cantidad de términos en idioma inglés es debido a que estas son las expresiones más usuales y conocidas, además muchas de éllas no han sido traducidas por no haber encontrado palabras en castellano con el sig nificado exacto; de todos modos se han traducido todas las expresiones que fueron posibles.

Por último, quisiera agradecer de manera especial a la Compañía EFYASA por haberme permitido tener acceso a

su equipo de Entrada de Datos marca Inforex y también a todo el personal que trabaja en el Laboratorio de esta compañía por haberme apoyado en todo sentido durante el desarrollo de este proyecto.

Asimismo, quisiera agradecer al Ing. Miguel Angel Martino por su desinteresada cooperación e importantes sugerencias y a todos los que de una u otra manera con tribuyeron para que este proyecto se hiciera una reali - dad. A todos, gracias.

### CAPITULO I

### INTRODUCCION

### 1.1 Consideraciones Preliminares

Gracias al avance tecnológico de nuestro siglo se ha logrado automatizar diversas tareas y procesos, los cuales eran largos y tediosos en el pasado; principalmente la aparición de la Computadora ha revolucionado y modificado los métodos de trabajo facilitando la tarea del hombre.

La gran capacidad de procesamiento de información de la Computadora ha dado nacimiento a la Informática, la cual abarca una gran cantidad de ramas y subdivisiones.

La Programación, una de las principales ramas de la in formática, es actualmente muy utilizada debido a su sencillez y eficiencia.

Mediante la programación podemos de una manera fá cilmente comprensible para cualquier persona comunicar - nos con un Computador y pedirle que ejecute determinadas órdenes tales como operaciones matemáticas complejas, que ordene y almacene una determinada cantidad de datos en su memoria, o que imprima una lista con los datos de una determinada cantidad de personas.

Todas estas tareas que hemos mencionado requieren de que previamente al procesamiento que se deba realizar, el Computador haya sido provisto de los datos que va a nece sitar para llevar a cabo la tarea requerida, es decir debe haber una entrada de datos previamente al procesa - miento. Como se puede ver esta Entrada de Datos es muy importante y depende de la exactitud de ésta el resultado que obtengamos del Computador.

Hay diversas maneras de introducir información al Computador, así como también hay diversos tipos de datos.

Básicamente, hay dos formas de introducir datos al computador: a) En línea, es decir, los datos son entrega dos al Computador directamente, mientras éste se encuentra realizando cualquier otra tarea. Como sabemos la en trada de datos es un proceso lento debido a que es efectuado por el hombre, entonces el computador tiene que com partir su tiempo entre recepcionar el dato que está troduciendo el operador de entrada de datos y ejecutar cualquier otra acción. Actualmente, muchos computadores modernos usan este sistema pero ésto no indica necesaria mente que al estar el Computador atendiendo otras operaciones más complicadas no atiende eficientemente la entrada de datos haciendo este proceso aún más lento; b) Fuera de Linea, en este método todos los datos que van a ser procesados son almacenados en un medio grande de almacenamiento completamente independiente del Computa dor; es decir, es un sistema inteligente independiente de entrada de datos, por lo general estos sistemas tienen una capacidad mínima de procesamiento y se limitan a ordenar los datos en un bloque jerárquico bien definido. Este sistema al igual que el anterior tiene sus ventajas y desventajas; obviamente al estar este pequeño sistema enteramente abocado a controlar la entrada de datos no va a introducir ningún retardo como en el caso anterior; su desventaja sería que cuando se quiere procesar la información hay que hacer llegar de alguna manera al Computador los datos, claro que estos datos ya se encuentran completamente listos, compatibles, para ser leídos por él; pero aún así ésto representa de algún modo intervención de un operador, del programador, en transportar los datos de un lugar a otro.

Concretamente nuestro trabajo se centra en el diseño de uno de estos pequeños Sistemas Inteligentes de Entrada de Datos, es decir, un sistema independiente que

recibe datos, que trabaja fuera de línea (Off Line en la

literatura inglesa), que ordena la información previamen

te a su almacenamiento definitivo.

Este sistema de Fuera de Línea si bien puede pare - cer en desventaja con respecto al sistema En Línea puede convertirse muy ventajoso en determinadas aplicaciones tales como aquellas que requieren introducir información masivamente por un tiempo prolongado para hacer el procesamiento luego de ese tiempo; éste es un ejemplo típico de las transacciones comerciales, donde se requiere dia-

riamente introducir registros de información respecto a ventas o pagos y al final del año se requiere hacer el Balance de todas las operaciones mercantiles; igualmente en el caso de las planillas de pagos diariamente a lo lar go de un mes se introduce información respecto a cada em pleado de una Compañía X con sus datos personales, números de carnet de identificación, sueldo, etc. y a esta información se la va actualizando con los descuentos que tal o cual empleado pueda tener, los aumentos, horas extras, etc.; entonces al final del mes se traslada la información al Computador para su procesamiento, por ejemplo, mandar a imprimir las planillas de pago, sacar una lista del balance de determinada compañía o cualquier otra cosa que se requiera.

En general, los lugares en que se requiere un siste ma tal como éste, que permite una entrada masiva de información para un procesamiento posterior no determinado son muchos. Podemos citar como ejemplo a todas las Instituciones gubernamentales que controlan determinados sectores económicos a nivel de todo el país, es decir, los Ministerios, éllos requieren de un sistema que les permita llevar una relación ordenada de toda la información que

de todos los asegurados a nivel nacional y requieren en cada momento actualizar el estado de cada uno de estos asegurados según las prestaciones que reciban éstos por parte del Seguro, en este cas este sistema de entrada de datos es de vital importancia.

## 1.2 <u>Descripción de un Sistema independiente de Entrada</u> de Datos

Seguidamente describiremos las principales partes y características de un sistema de entrada de datos del que hemos estado tratando. Primeramente, trataremos a grandes rasgos las partes de un Sistema de Entrada de Da tos y luego nos centraremos en un sistema ya existente, el cual ha servido como fuente de referencia para el desarrollo del presente trabajo.

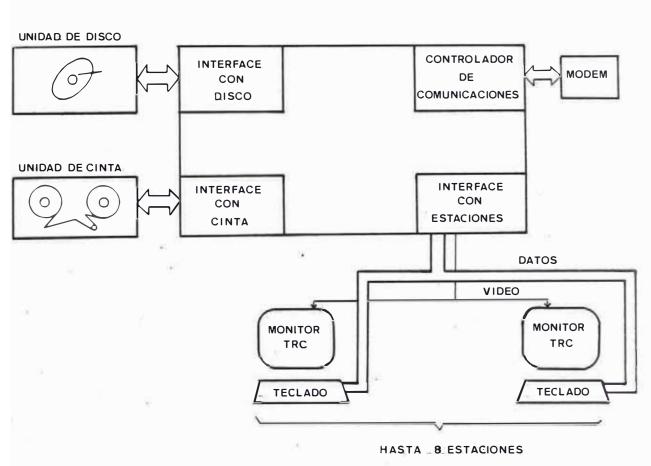

Un Sistema de Entrada de Datos consta básicamente de 4 elementos:

- A) Unidad Central

- B) Sistema de Almacenamiento Temporal

- C) Sistema de Almacenamiento Final

- D) Organos Terminales de Entrada de Datos

- A) Unidad Central; también llamada CPU (Unidad Central de Proceso), es la que comanda todas las operacio nes del sistema, es el órgano inteligente que mediante un determinado programa almacenado realiza todas las operaciones. Esta Unidad Central también comprende aquellos elementos que le van a servir para interaccionar con las

tres partes restantes del Sistema. Estos elementos deno minados Interfaces hacen posible la comunicación de los otros sistemas con el CPU.

- B) Sistema de Almacenamiento Temporal; es aquel dis positivo en el cual el CPU almacena los datos que está recibiendo a través de los Organos Terminales de Entrada de Datos. El almacenamiento en este dispositivo es temporal, no defnitivo, es susceptible de ser modificado rá pidamente antes de ser almacenado en el Dispositivo de Almacenamiento Final. La importancia de este medio de Almacenamiento Temporal es obvia, cuando se ingresan datos importantes en forma masiva es necesario verificar los datos en algunas ocasiones hay que modificar y en otras hay que insertar nueva información; este medio de Almacenamiento Temporal nos provee un acceso rápido a la información en todo momento.

- C) Sistema de Almacenamiento Final; es aquel dispositivo en el cual se almacenan los datos que previamente han sido introducidos al Sistema de Almacenamiento final, han sido verificados y se requiere liberar al sistema de Almacenamiento Temporal para introducir en él más información. Este sistema debe consistir en un medio seguro de almacenamiento de información por un período no de terminado.

- D) Organos Terminales de Entrada de Datos; vienen a ser la interface entre las operaciones de entrada de datos y la Unidad Central. Generalmente, son varios lo

cual permite tener varios operadores introduciendo datos al mismo tiempo. La Unidad Central se encuentra haciendo un polling de todos los terminales recepcionando los datos. El dispositivo más comúnmente utilizado para este fin es el Teclado, el cual puede ser de diversos tipos.

### 1.3 <u>El Sistema Inteligente de Entrada de Datos de</u> Inforex

Como se ha dicho anteriormente, el presente trabajo ha sido desarrollado siguiendo los conceptos generales de un equipo de Entrada de Datos ya existente, el cual debi do a su antiguedad hace uso de una tecnología ya obsoleta, lo cual acarrea actualmente muchos problemas en su uso. El presente trabajo ha sido desarrollado utilizando íntegramente un diseño propio pero buscando llegar a los mismos atributos y opciones que tiene el Sistema de Entrada de Datos de Inforex. Tanto el Hardware como el Software difieren en ambos pero los objetivos y resultados son los mismos.

En base a la descripción que hemos hecho en el acápite anterior respecto a las partes fundamentales de un Sistema Independiente de Entrada de Datos, vamos a explicar la constitución básica del Sistema Inforex con lo cual será fácil entender la constitución del diseño del presente sistema.

La Unidad Central del Sistema Inforex está totalmen

te implementado con Circuitos Integrados del tipo Diodo Transistor (Lógica DTL), los cuales son de baja escala de integración, lo que da por resultado circuitos impresos de grandes dimensiones y gran consumo de corriente. Actualmente, la tecnología DTL está prácticamente en des uso a sus limitaciones en cuanto a velocidad y escala de integración a la par que se caracteriza por consumir mayor potencia.

Entonces, dentro de su Unidad Central posee un grupo de tarjetas, cada una con una función específica. La

más importante, llamada Procesador viene a ser el cora zón de la Unidad Central, el cerebro que dirige a los de

más elementos de la Unidad Central y por tanto también a

los periféricos. También hay tarjetas de Interface con

los periféricos.

Hasta ahora no hemos detallado la constitución de los sistemas de Almacenamiento Temporal y Final. Concre tamente el Sistema Inforex, el Sistema de Almacenamiento Temporal, está conformado por un Disco Magnético con capacidad de almacenamiento de hasta 5 Megabytes. Una Uni dad de Disco Magnético provee un almacenamiento masivo de información, la cual puede ser accesada rápidamente debi do a sus características mecánicas. En un capítulo posterior definiremos los principios fundamentales de una Unidad de Disco con lo cual será fácil comprender los pasos y criterios seguidos en el diseño de la Interface co rrespondiente.

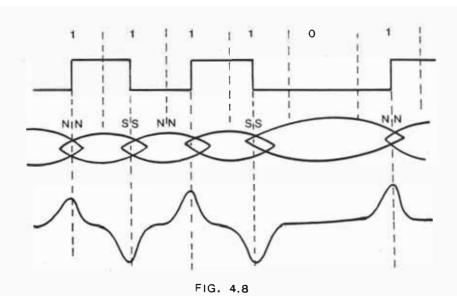

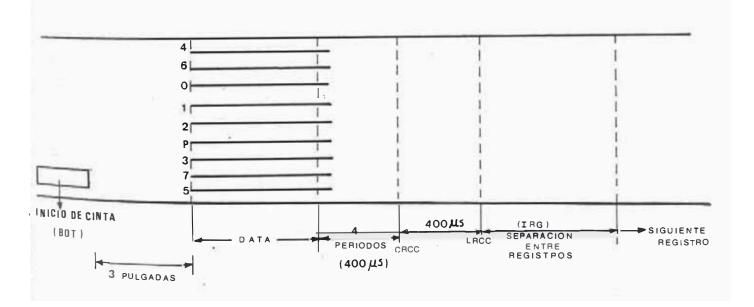

El Sistema de Almacenamiento Final está constituido por una Unidad de Cinta Magnética. Las principales ca racterísticas de esta Unidad de Cinta son: la densidad de grabación es de 800 bits por pulgada (BPI) y la veloci dad de desplazamiento de la cinta es de 12.5 pulgadas por segundo. Esta Unidad de Cinta Magnética posee nueve pis tas a lo largo de las cuales se graba información median te cambios de flujo magnético. Estas pistas son también llamadas Tracks. En un capítulo posterior se dará definiciones completas de la Unidad de Cinta. La razón de porque se usa Cinta Magnética como medio de Almacenamien to Final es debido a la confiabilidad de la Cinta en retener información por largos períodos de tiempo, es fácilmente archivable, no ocupa mucho espacio y tiene una gran capacidad de almacenamiento.

El acceso a la información en la Unidad de Cinta es más lento que en el Disco pero ésto no es de importancia ya que la información en la Cinta no es continuamente re querida sino solamente en el momento que se van a realizar el procesamiento de todos los datos en forma masiva.

Dentro de la Unidad Central hay también una tarjeta que sirve de Interface con la Unidad de Cinta Magnética y otra tarjeta que sirve de Interface con la Unidad de Disco Magnético. Adicionalmente, el sistema posee una Memoria de Ferrita con capacidad de hasta 12 K bytes; es ta memoria comprende dos tarjetas independientes, una de las memorias es solamente usada para lectura del sistema

operativo y la otra es usada como memoria de escritura y lectura, es decir, como memoria de trabajo. Estas dos memorias vienen a ser el equivalente de la memoria ROM y la memoria RAM respectivamente.

El Sistema Operativo está normalmente residente en el Disco Magnético pero mediante una rutina de inicialización es traído desde el disco a la memoria de sólo lec tura que es de donde el Procesador va a tomar todas las instrucciones que debe realizar durante la operación del sistema.

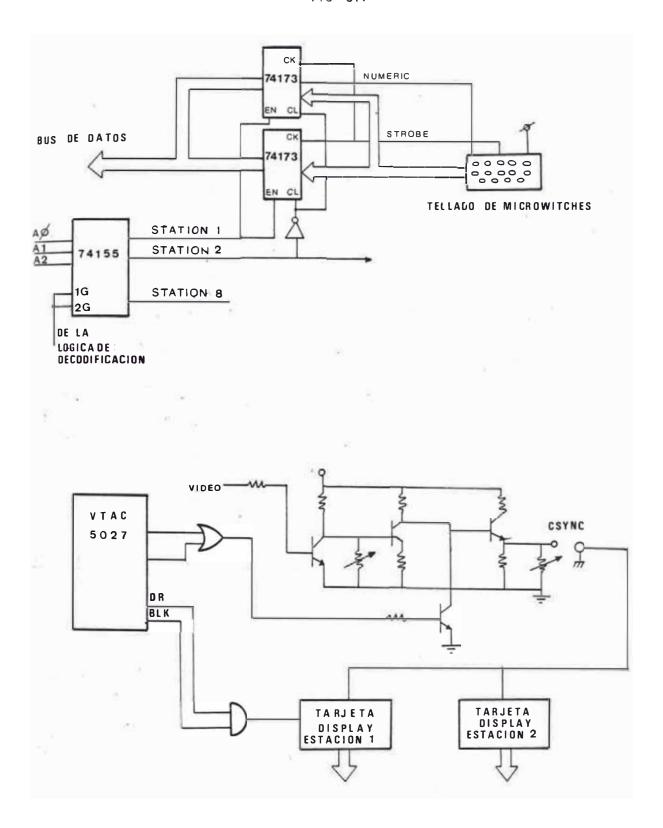

El Sistema Inforex trabaja con ocho terminales de entrada de datos a la vez, estos terminales también reciben el nombre de estaciones, y cada una consta de una pantalla de tubo de rayos catódicos y un teclado de Microswitches a través del cual se introducen los datos y el operador puede ver en la pantalla los caracteres que está digitando.

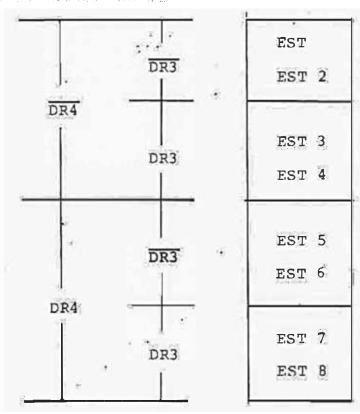

Cada estación además posee una tarjeta de circuito impreso llamado Tarjeta de Estación, la cual sirve de interface entre la Unidad Central y la Estación; esta tar jeta contiene unos registros en las cuales se almacena el dato de 8 bits que proviene del teclado. Todas las estaciones son rastreadas 60 veces por segundo de acuerdo a la constitución del Sistema Operativo.

La Unidad Central posee para esto una tarjeta llama da Interface de Estaciones, la cual controla a través del

Procesador la toma de datos de todos los teclados y su almacenamiento en posiciones definidas de memoria, con - trola además la generación del video que va hacia todas las pantallas de los terminales. Es conveniente además detallar que las 8 estaciones con las cuales trabaja el sistema están conectadas en una configuración de cadena, es decir, cada estación recibe todas las señales de control necesarias desde la estación que le precede y a su vez envía estas mismas señales a la estación que le sique en orden.

### 1.4 <u>Descripción Básica de la Constitución del Sistema</u> Diseñado

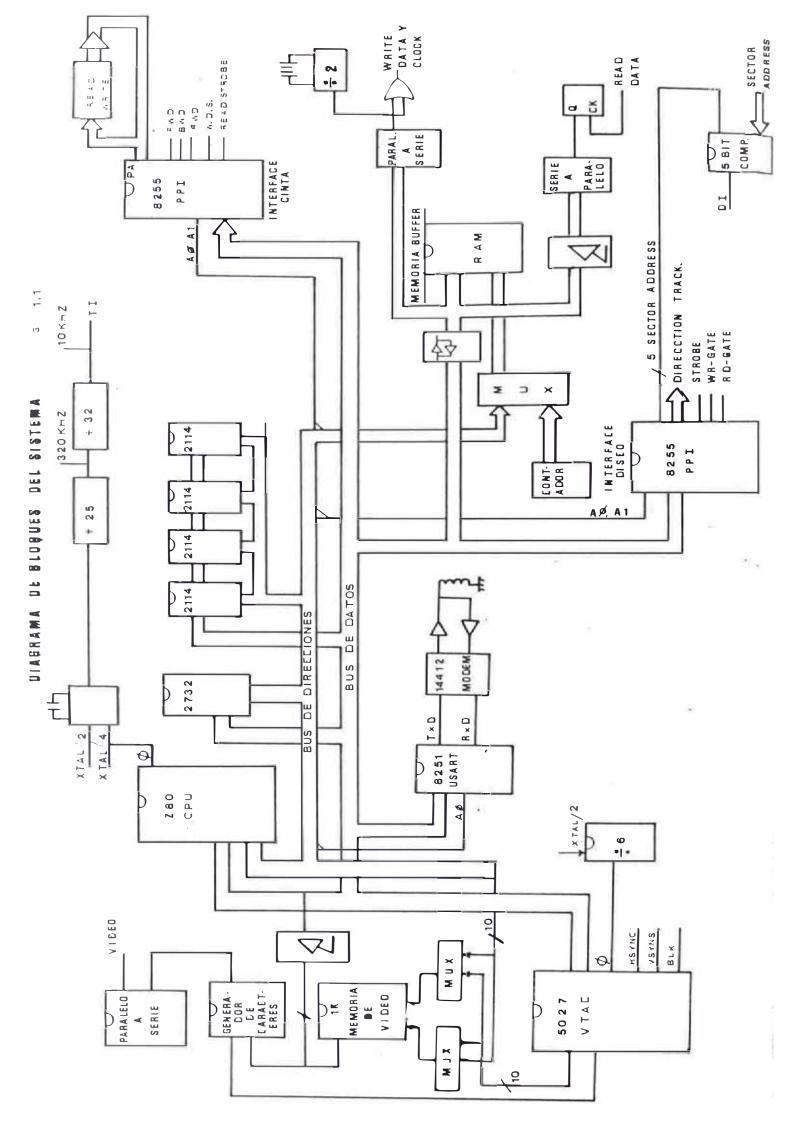

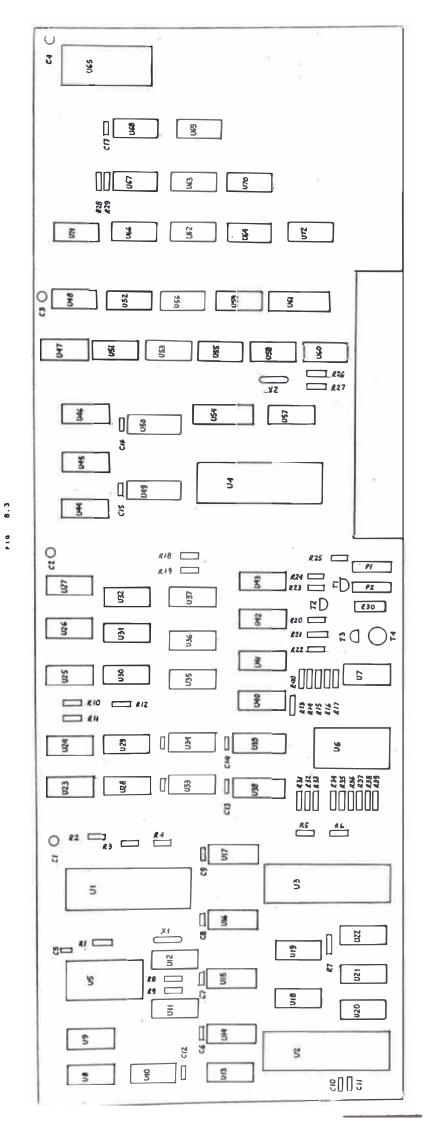

La constitución básica en cuanto al Hardware del presente sistema materia de este trabajo puede verse en el diagrama N° 1.1. Todo el sistema se puede dividir en 5 partes fundamentales, cada una de las cuales estudiare - mos con mayor detalla en el capítulo siguiente.

1) El procesador o corazón de la Unidad Central está formado por el Microprocesador Z-80, el cual ejecuta

el Sistema Operativo que se encuentra en la memoria EPPOM

2732 que tiene una capacidad de 4 K x 8 bits. El procesador también posee una memoria de trabajo de 2K x 8 bits.

El clock con que trabaja el Procesador es derivado de un

cristal de 7.98336 Mega Hertz, el cual es dividido entre

2 con lo cual se obtiene aproximadamente 4 MHz, los cuales alimentan directamente al procesador de tipo Z80-A

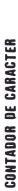

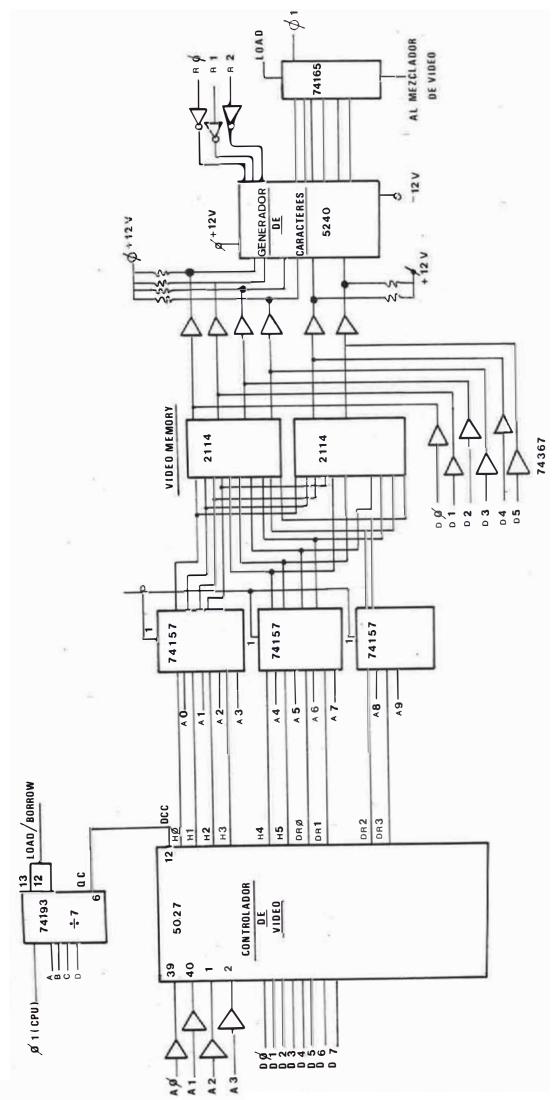

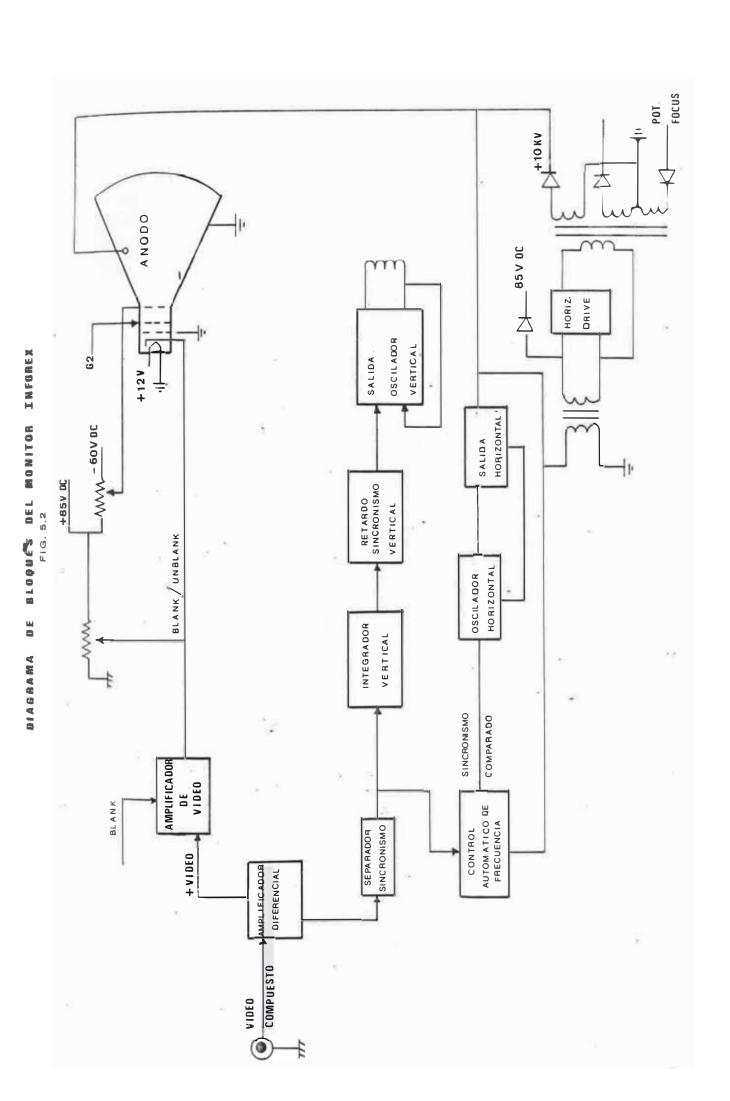

Dentro de esta Unidad Central también se considera a la circuitería que proporciona el video; la generación de - éste está básicamente controlado por el VTAC-5027 el que es un circuito integrado específicamente diseñado con es tos fines, se cuenta además con una memoria de 1K x 8 lla mada memoria de Video, que direcciona al generador de caracteres seleccionando así los caracteres que deben aparecer en pantalla, la salida del generador de caracteres es serializada y combinada con los pulsos de sincronismo vertical y horizontal es enviada a todas las estaciones. En el siguiente capítulo se describirá en detalle esta Unidad Central.

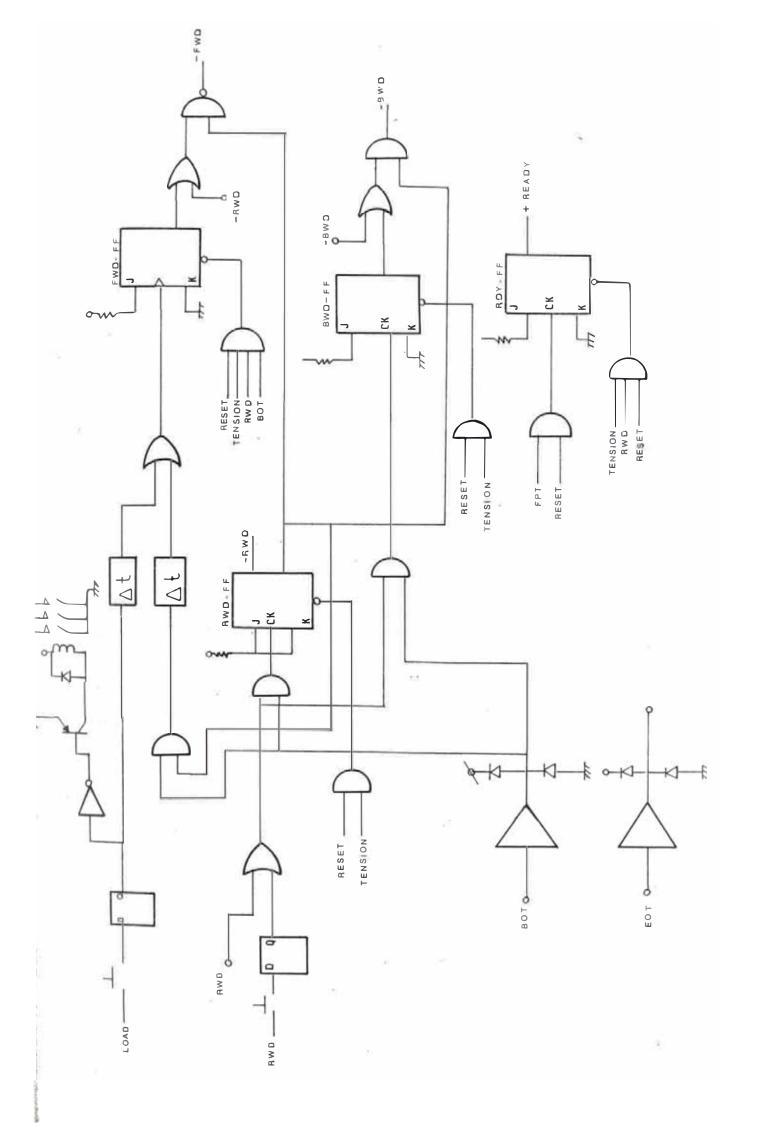

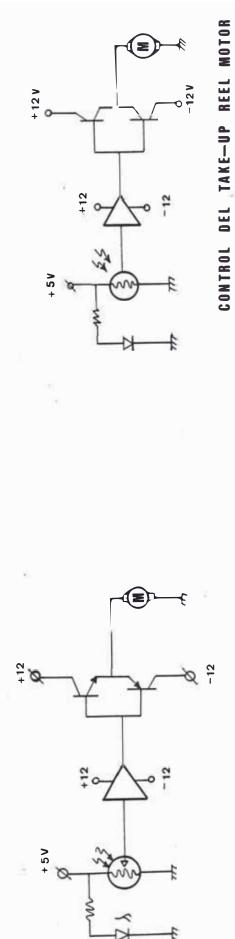

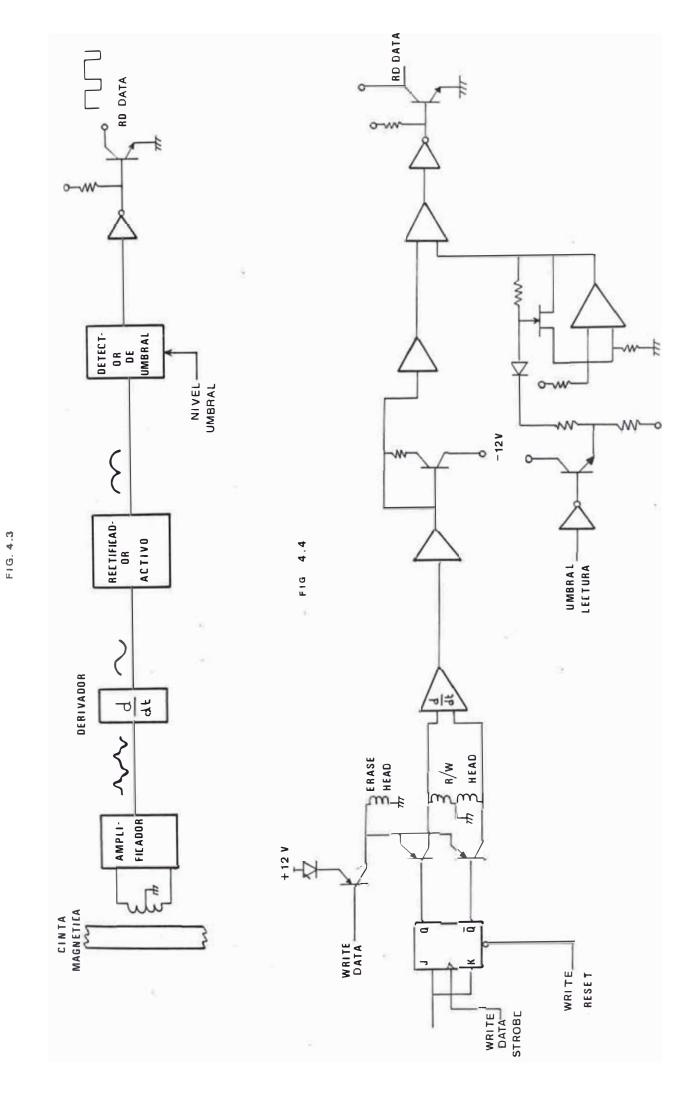

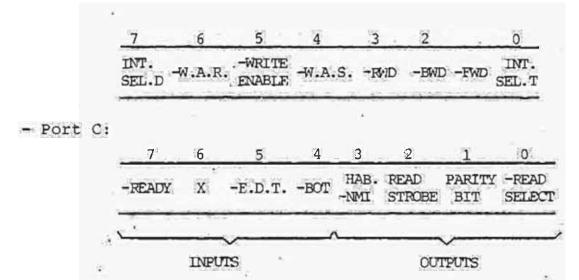

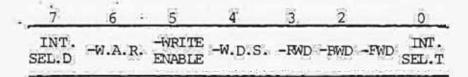

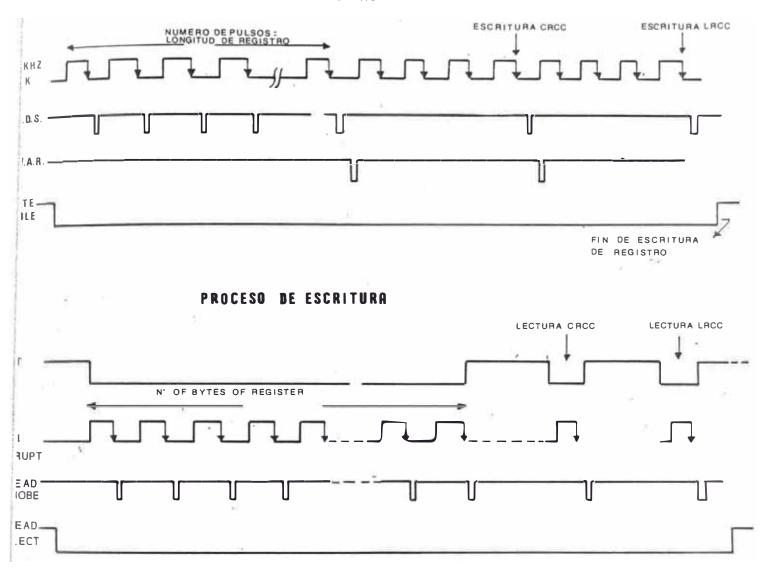

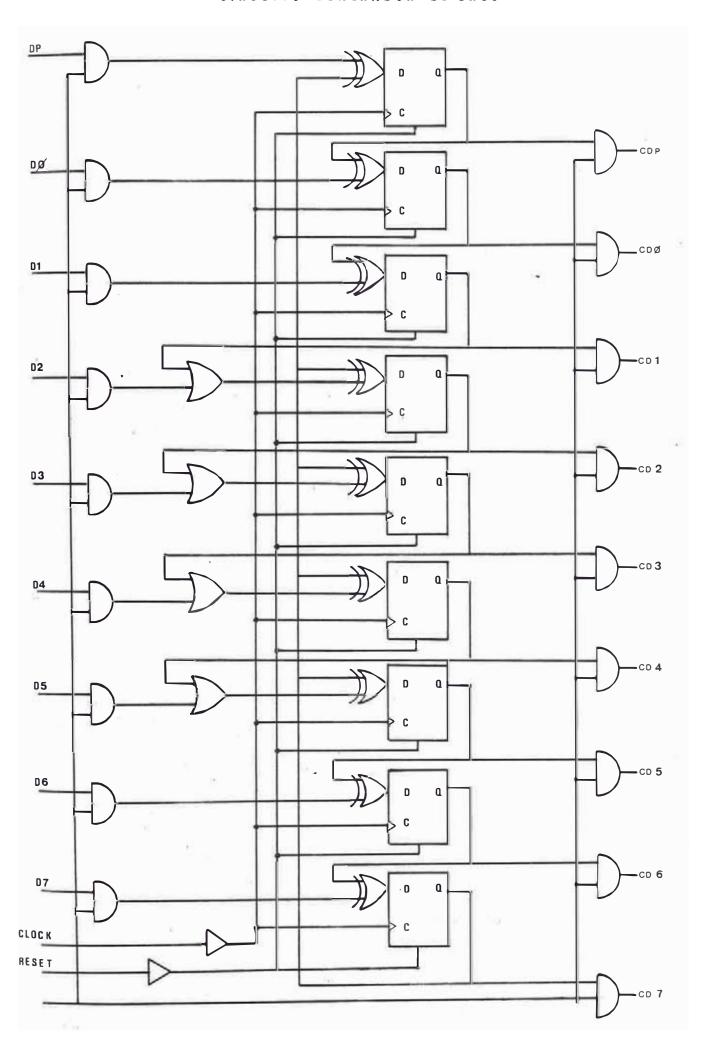

2) Interface con la Unidad de Cinta; está prácticamente centralizada en el circuito Integrado 8255 PPI (Interface de Periférico Paralelo). Como sabemos, el 8255 PPI posee tres ports de 8 bits cada uno, los cuales pueden ser programados como entradas o salidas independientemente con lo cual poseemos gran cantidad de señales de control ya sea de entrada o salida. La Unidad de Cinta con la que se trabaja (Unidad de Cinta del Sistema Inforex) es un periférico Paralelo por lo cual el 8255 se presta convenientemente para esta aplicación. Es importante adelantar que siendo la Unidad de Cinta un sistema de acceso lento la mayoría de las operaciones con ella son totalmente controladas por el Procesador a través del Sistema Operativo. Adicionalmente, hay una lógica combinacional que sirve para sincronizar la lectura con el

るかはある方の他ははなければから時には

inicio de cada bloque de información (con cada registro). También la Interface con la Unidad de Cinta comprende una cadena de contadores, los cuales a partir del clock del Procesador generan una señal de 10 KHz, la cual esta blece la velocidad de grabación y lectura en la cinta, es decir, determina la densidad de grabación. En el capítulo correspondiente detallaremos sobre la constitución de esta interface e igualmente describiremos cómo el sis tema operativo hace uso de todo este Hardware para inter accionar con la Cinta.

3) Interface con la Unidad de Disco; debido a la ve locidad de transferencia de información con la Unidad de Disco, la mayoría de las operaciones ya no son controladas por Programa tal como en el caso de la Interface de Cinta sino mas bien por Hardware, por lo cual tal como en el caso de la Interface de Cinta sino mas bien por Hardware, por lo cual éste se ha complicado notablemente. Básicamente esta Interface consta de una lógica de Acceso Directo a Memoria (DMA), para lo cual se dispone una memoria RAM con una capacidad de 1 K x 8, la cual sir ve de almacenamiento transitorio, esta memoria puede ser accesaria tanto por el Procesador como por la lógica de DMA en si, teniendo ambos la capacidad de leer o escri bir en élla. Siendo el Disco un Periférico Serial la lógica de DMA incluye un conversor serie-paralelo para etapa de lectura y un conversor paralelo-serie para la etapa de escritura.

La Interface con la Unidad de Disco trabaja con un reloj distinto al reloj de la Unidad Central debido a que la velocidad de transferencia de información con el Disco viene exactamente especificada por el fabricante igual a 2.5 MHz. y esta frecuencia no puede ser derivada del reloj del Procesador. Usando entonces un cristal re sonante en 10.0000 MHz por divisiones sucesivas deriva — mos la frecuencia requerida de 2.5 MHz.

Adicionalmente a las señales de escritura y lectura de datos las cuales son seriales e independientes una de otra hay una serie de otras señales de control ne cesarias para poder accesar al Disco, debido a esto hace uso nuevamente del 8255 PPI (Interface Periférica -Programable) para controlar estas señales que pueden ser manejadas a la velocidad de trabajo del Procesador. Como se puede ver en el Diagrama N° 1.1 el bus de datos de la memoria que sirve de Buffer en la lógica de DMA se co munica con el bus de datos del Procesador a través de Driver de 3 estados bidireccionales, lo cual permite que en el momento que ocurre el acceso directo a memoria el Procesador se independiza de esta memoria. En un capítu lo posterior describiremos en detalle la constitución de la lógica de DMA así como el Sistema Operativo controla el 8255 PPI durante la transferencia con el Disco.

4) Organos de entrada de datos; la entrada de datos se efectúa a través de las Estaciones Terminales. El sistema puede trabajar hasta con ocho de estas. Cada

Estación Terminal consta de un teclado con una distribución de caracteres similar a la de una máquina de escribir convencional, un monitor o pantalla con su tarjeta incorporada y la tarjeta de Estación. Esta tarjeta de Estación se encarga de almacenar en un par de registros three-state el dato digitado en el teclado, el cual se encuentra codificado en 8 bits. El Procesador durante - la rutina de toma de dato habilita estos registros para leer el caracter. Este rastreo lo efectúa, según el Sis tema Operativo, 60 veces por segundo en concordancia con el pulso de Sincronismo Vertical.

La Tarjeta de Estación posee además una lógica - combinacional mediante la cual selecciona las filas de caracteres que deben displayarse en el monitor de tal es tación. Como se explicará más adelante, la Unidad Central envía al cable coaxial de video información paralas ocho estaciones a la vez, corresponde a la Tarjeta de Estación seleccionar filas de caracteres predeterminadas según una distribución de la memoria de video que se explicará en un capítulo posterior.

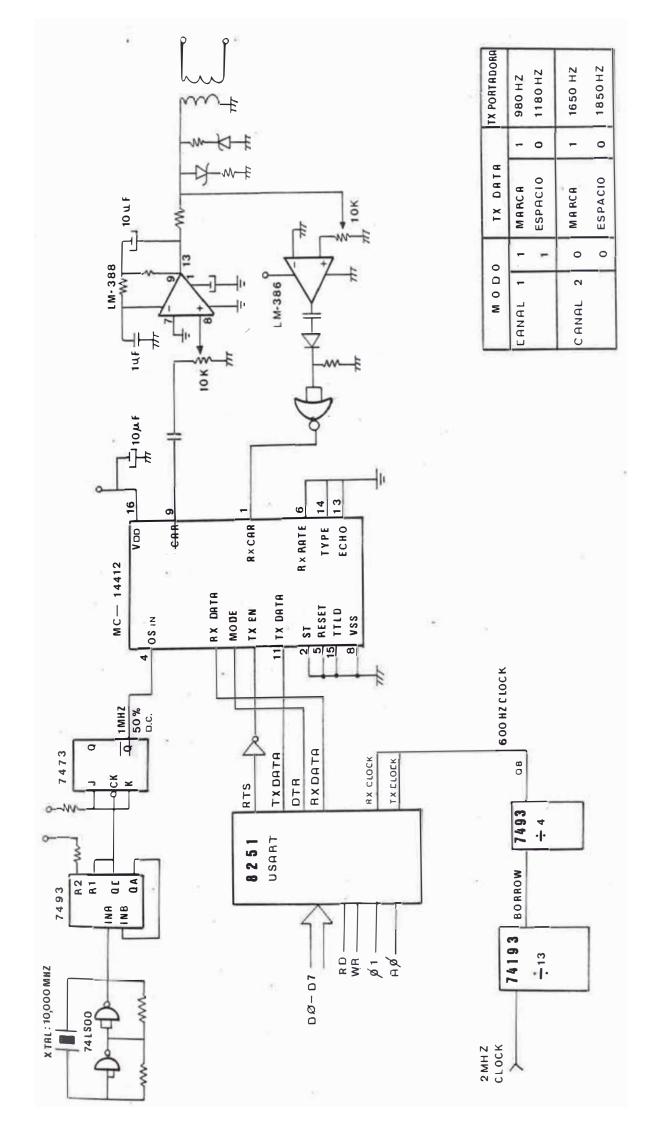

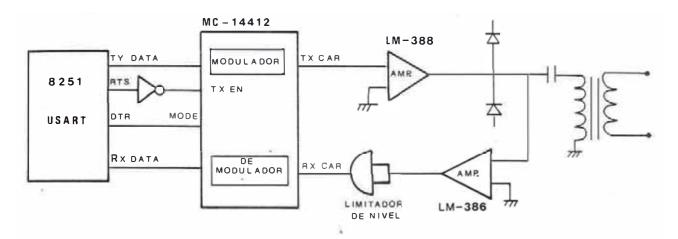

5) Opción de Comunicaciones; la comunicación serial que efectúa el sistema está controlada básicamente por el Circuito Integrado 8251, Interface Programable de Comunicaciones, la forma de trabajo del 8251 en cuanto al tipo y formato de la transmisión es programada por el procesador, asimismo el Procesador envía el dato a transmi-

tir mediante el bus de datos, el 8251 serializa este byte a la vez que habilita una serie de señales de control las cuales están diseñadas para interactuar con un Terminal de Comunicaciones, tal como un Modem (Modulador-Demodula dor). La opción de comunicaciones incluye un conector RS-232 con el que podemos conectar el sistema directamen te a un Modem y poder así transmitir por línea telefónica.

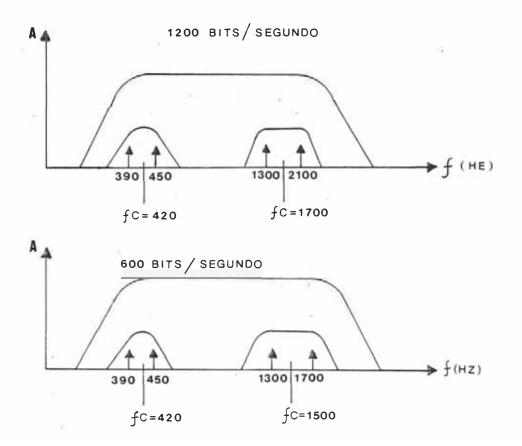

Incluido dentro de nuestro sistema tenemos una circuitería que simula un Modem de baja velocidad; básicamente consta de un generador F.S.K. el cual recibe los datos en forma serial del 8251 y genera tonos de frecuen cias correspondientes para el uno lógico y para el cero lógico; estos tonos son amplificados antes de ser acopla dos a la línea telefónica a través de un transformador adaptador de impedancias.

Durante recepción se efectúa el proceso inverso, una vez amplificados y convertidos en pulsos digitales - los tonos de pequeña amplitud que vienen por la línea te lefónica, son convertidos en unos y ceros lógicos por el Modem y posteriormente entregados al 8251.

El Protocolo que se usa durante la Comunicación es el B.S.C. (Comunicación Binaria Síncrona).

#### CAPITULO II

### LA UNIDAD CENTRAL DEL SISTEMA

### 2.1 Fundamentos de la Unidad Central

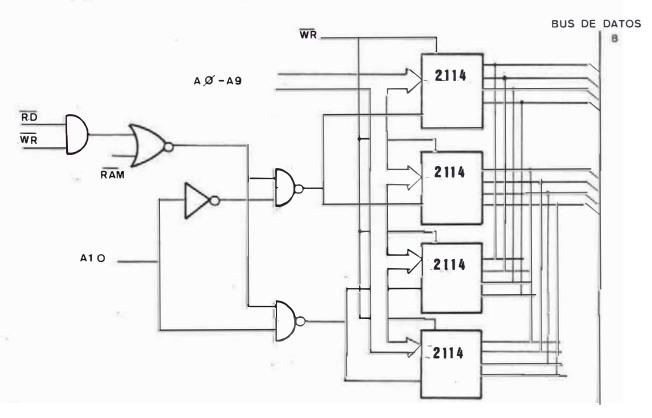

La Unidad Central está conformada por el Z-80 CPU - el cual comanda todas las funciones del sistema a través de un sistema operativo residente en memoria EPROM-2732, la cual tiene una capacidad de 4K bytes. Asimismo, el CPU trabaja con una memoria RAM 2114 agrupada en un banco de 2 K bytes, en esta memoria de trabajo se almacena temporalmente el registro que está siendo digitado en ca da estación; en ella se encuentra también los programas de digitación correspondiente a cada estación, asimismo se usan determinadas posiciones como registros auxilia - res durante la ejecución del sistema operativo. La descripción detallada de cada uno de estas localidades de memoria se da en el capítulo que trata del sistema operativo.

En la figura N° 2.1 se muestra la forma en que está dispuesta la RAM de trabajo y la lógica de decodificación que la selecciona.

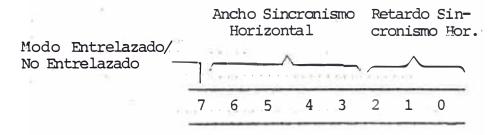

La Unidad Central también incluye al Controlador de Video 5027, êste es un dispositivo totalmente programa - ble por el CPU trabajando con instrucciones de entrada-salida, internamente está formado por nueve registros, -

### ELG. 2.1 SELECCION DE MEMORIA RAM

los cuales determinan todas las características de la trama a displayar en la pantalla.

Los pines contadores de caracteres y de fila de caracteres alimentan a la memoria de video proveyendo de este modo continuamente información al generador de caracteres; el CPU también puede accesar a la memoria de video para hacer un refresh, el sistema operativo efectúa este refresco inmediatamente después de recibir una interrupción por parte del pulso de sincronismo vertical proveniente del Controlar de Video, asimismo la toma del dato del teclado también se efectúa a esta misma razón, es decir a 60 veces por segundo, valor que corresponde al pulso de sincronismo vertical.

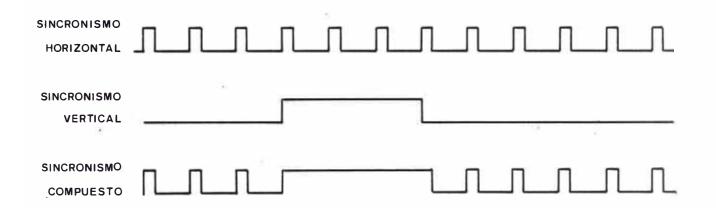

Las salidas del generador de caracteres son carga - das en un conversor paralelo-serie el cual alimenta a una circuitería a transistor, aquí son unidas la señal de vi deo y las señales de sincronismo. Formado el video compuesto, éste es transmitido a través de cable coaxial ha cia las estaciones terminales. Previamente la señal de video serializada proveniente del conversor paralelo serie es unida mediante una compuerta OR con la señal CUR-SOR, la cual es generada por el controlador de video.

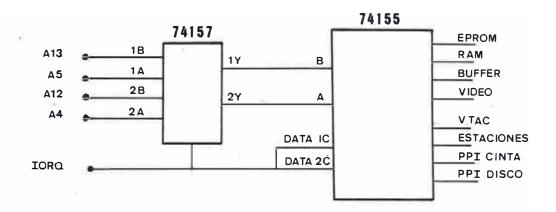

### 2.2 Direccionamiento y Decodificación del Sistema

Para evitar complicar el Hardware la decoficiación se centralizó en el 74155, decoder de 3 á 8 líneas, cu - yas salidas agregándoles una lógica combinacional simple

van a seleccionar a los ocho dispositivos con que consta el sistema, uno por vez. El Diagrama N° 2.2 nos muestra esta lógica de decodificación. Se observa que la señal IORQ mediante un Multiplexor selecciona los bits que direccionan al 74155, ésto quiere decir que cuatro disposi tivos van a ser trabajados en forma normal con instrumen tos de lectura y escritura, mientras que los otros cuatro van a ser trabajados o accesados con instrucciones de Entrada y Salida. En la Tabla siguiente se muestra cada dispositivo con su dirección, la cantidad de bytes que involucra y el tipo de instrucción con el cual es ac cesado.

|                 | The state of the s |       |             |                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|------------------|

|                 | N°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BYTES | DIREÇCION   | TIPO INSTRUCCION |

| EPRO <b>M</b>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4K    | 0000 - 0FFF | NORMAL           |

| RAM             | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2K    | 1000 - 17FF | NORMAL           |

| BUFFER          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1K    | 2000 - 23FF | NORMAL           |

| VIDEO           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1K    | 3000 - 33FF | NORMAL           |

| VTAC            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16    | XX00 - XX0F | ENTRADA - SALIDA |

| ESTACIONES      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 08    | XX10 - XX17 | ENTRADA - SALIDA |

| INTERFACE CINI  | 'A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 04    | XX20 - XX23 | ENTRADA - SALIDA |

| INTERFACE DISCO | ) !!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 04    | XX30 - XX30 | ENTRADA - SALIDA |

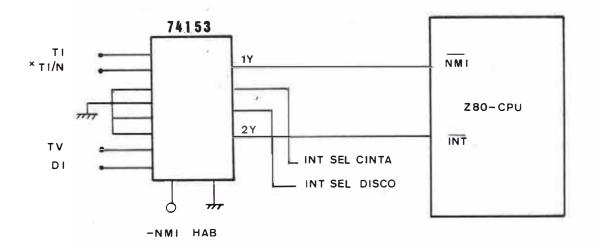

### 2.3 Lógica de Interrupciones

Hay varias señales que son usadas para interrumpir al Procesador. La mas usada es la señal TV, derivada del pulso de sincronismo vertical que genera el VTAC-5027, -

LOGICA DE INTERRUPCIONES \_\_FIG 2.3

|            | ASEL | BSEL | SEÑAL | SELECCIONADA |

|------------|------|------|-------|--------------|

|            | , 1, | 1    |       | T I          |

| 701<br>2 E | 0    | 1    |       | TI/N         |

| K-1        | 1 .  | 1    |       | ΤV           |

|            | 1    | 0    |       | DI           |

que es la que sincroniza todas las operaciones durante - el trabajo normal, esta señal va conectada al pin de Interrupción Enmascarable (INT). Durante la ejecución de una operación de transferencia con el disco se debe tener la señal DI conectada al pin INT para que el procesa dor sepa cuando las cabezas de lectura/escritura se encuentra sobre el sector especificado.

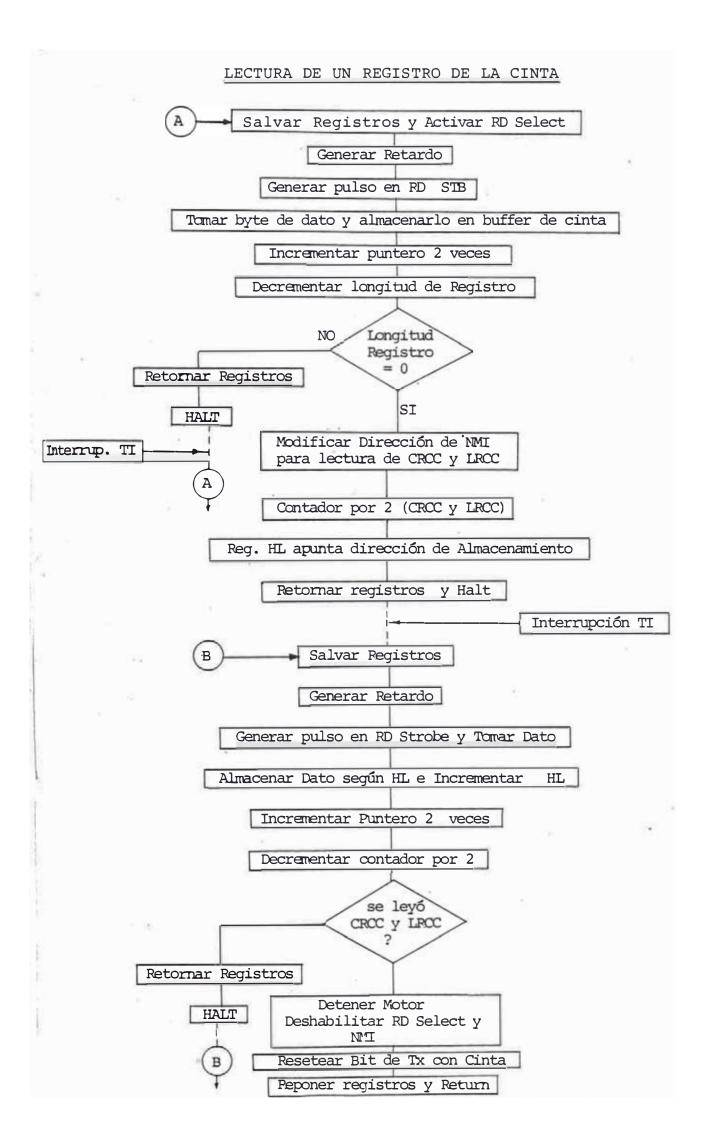

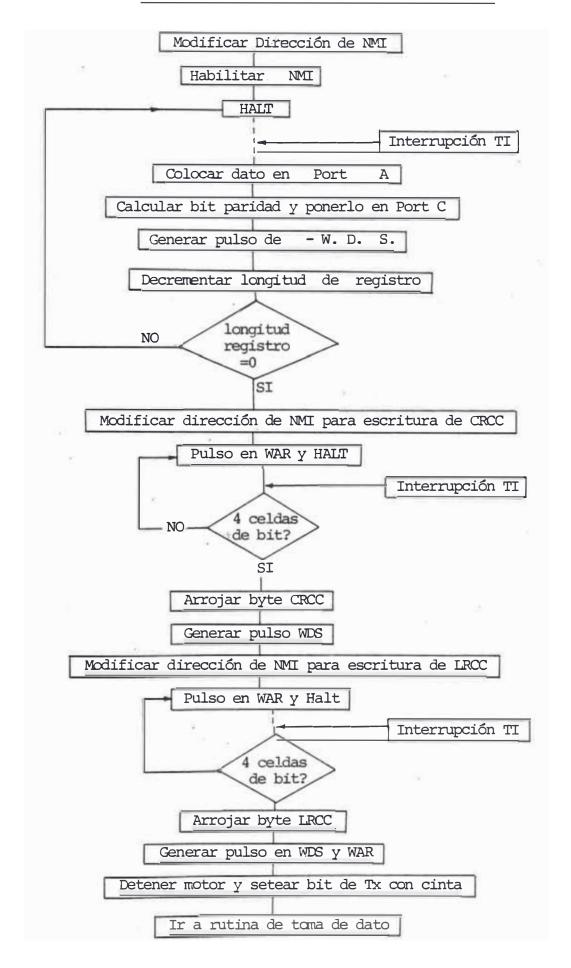

Por otro lado, durante una transferencia con la cin ta se requiere que la señal TI (10 KHz) se conecte a la entrada NMI del Procesador (Interrupción No-Enmascarable) para sincronizar la velocidad de lectura o escritura en la cinta.

Debido a esta complejidad en la selección de la señal de interrupción se decidió centralizar toda esta lógica en el doble multiplexor de cuatro canales 74153.

En la figura N° 2.3 se representa esta lógica de interrupciones, las señales INT. SELECT DISK e INT.SELECT TAPE se encargan de seleccionar uno de los cuatro cana - les de ambos multiplexores.

La salida de uno de los multiplexores está conectada a INT y la salida del otro está conectada a NMI. El 74153 posee además entradas de habilitación para cadamul tiplexor. El multiplexor que trabaja con las señales que accesan a INT posee su entrada de habilitación perma nentemente activada ya que esta interrupción puede ser deshabilitada mediante una instrucción del CPU. En cam-

bio, las señales que originarán un NMI dependen de que - esté habilitada la señal NMI HAB, de esta forma se puede contralar la ocurrencia de una interrupción no-enmascara da.

La interrupción no-enmascarada se produce solamente al momento de hacer una transferencia con la cinta. La señal TI que produce esta interrupción proviene de una serie de contadores alimentados con el mismo reloj del CPU. Se pensó usar otra señal llamada TI/N, de un perío do mucho mayor que TI, para obtener la cuenta de estabilización de los motores de la Unidad de Cinta, pero posteriormente se descartó esta posibilidad.

Hay pues solamente una señal capaz de producir NMI y 2 señales capaces de producir INT como se muestra en la fig. N $^{\circ}$  2.3.

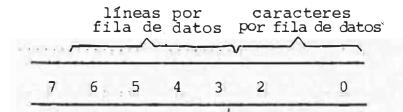

### 2.4 Sistema de Video

Como dijimos anteriormente, el sistema de video cons ta principalmente del Controlador de Video 5027, el cual es un circuito integrado programable, contiene 9 regis - tros en los cuales está contenida toda la información ne cesaria para displayar en la pantalla el cuadro requerido, es decir, el número de filas de caracteres, el número de caracteres de cada fila, las características de los pulsos de sincronismo vertical y horizontal, además también se programa la posición exacta en la cual debe aparecer el cursor en el cuadro, es decir, en qué fila

de caracteres y en qué caracter. El 5027 requiere alimentado con un clock de una frecuencia iqual al conta dor de caracteres, a partir de esta señal generará median te una cadena de contadores una cuenta binaria que puede constar hasta de 7 bits, la cual nos indica el caracter que está siendo displayado en ese instante; además, igual mente nos provee de una cuenta la cual puede constar hasta 5 bits que nos indica el número en binario de fila de caracteres que está siendo rastreada en ese instante. Estas dos cuentas binarias son usadas para direc cionar a la memoria de video, la cual contiene los códigos en formato ASCII de los caracteres que queremos displayar. Este direccionamiento está en verdad compartido (como podemos ver en el diagrama correspondiente) los bits de Direcciones del CPU a través de multiplexo res; es así como tanto el Z-80 CPU como el Controlador de Video 5027 pueden direccionar a la RAM de Video. Cuan do el CPU quiere hacer un refresco de la memoria de video, es decir quiere modificar o actualizar los caracteres que deben aparecer en la pantalla, hace una instrucción de carga direccionando a la memoria de video, hace que se active la señal VIDEO, la cual selecciona en el multiplexor las señales de direcciones del CPU, en este momento el CPU escribe en la memoria de video ിറട 1K bytes de los cuales consta esta memoria. Pero, la ma yor parte del tiempo la señal -VIDEO no se encuentra activa y es el Controlador de Video el que se encuentra le

yendo la memoria, a su vez la memoria entrega este byte leido al Generador de Caracteres, el cual posee 6 neas de entrada pudiendo formar  $2^6 = 64$  combinaciones, una combinación para cada caracter a displayar. El Gene rador de caracteres produce para cada caracter un conjun to de 5 x 7 puntos. El Controlador de Video además proveernos la cuenta de los caracteres y la cuenta de las filas de caracteres también produce mediante tres la cuenta de las filas de puntos (7 filas para nuestro caso por ser nuestro generador de caracteres del formato 5x7 puntos); estos tres bits se dirigen directamente generador de caracteres para seleccionar la fila de puntos correspondiente al caracter que está siendo seleccio nado en ese momento por los 6 bits provenientes de la me moria de video. Los 5 bits de salida del Generador de Caracteres son introducidos a un Conversor Paralelo-Serie el cual es alimentado con un clock igual a la frecuencia de puntos, es decir, una frecuencia igual a 6 veces frecuencia del contador de caracteres.

La salida de este conversor se suma con la señal CRV (Cursor Video) y este resultado se mezcla con la señal de sincronismo compuesta.

# CAPITULO III

#### DESCRIPCION DE LA UNIDAD DE DISCO

# 3.1 La Unidad de Disco marca Diablo

El presente sistema hace uso de la unidad de disco modelo 44B marca Diablo, el cual provee hasta 100 mega - bits de almacenamiento y está diseñado específicamente - para pequeños computadores de propósitos generales.

Posee 2 discos en su interior, uno fijo y el otro removible. Posee una velocidad de transferencia de datos de 25 MHz.

A continuación se especifican las características de esta Unidad de Disco:

- Densidad de Tracks : 200 tracks por pulgada (TPI)

Medio de Almacenamiento (Disco):

Tipo 5540 disco fijo y removi

ble

Diámetro del disco: 14 pulga-

das

- Técnica de Grabación Doble frecuencia

Cantidad total de tracks:

1632 (400 mas 8 disponibles en

cada superficie de cada disco)

- Capacidad en Bits: Total 100,000,000

Por disco 50,000,000

Por pulgada 2200

Por cilindro 250,000

Por track 62,500

- Tiempo de Acceso: De track a track 8 ms

Promedio 38 Ms

- Velocidad de rotación: 2,400 RPM con una tolerancia de 5%

- Velocidad de transferencia de cada bit: 2500 KHz.

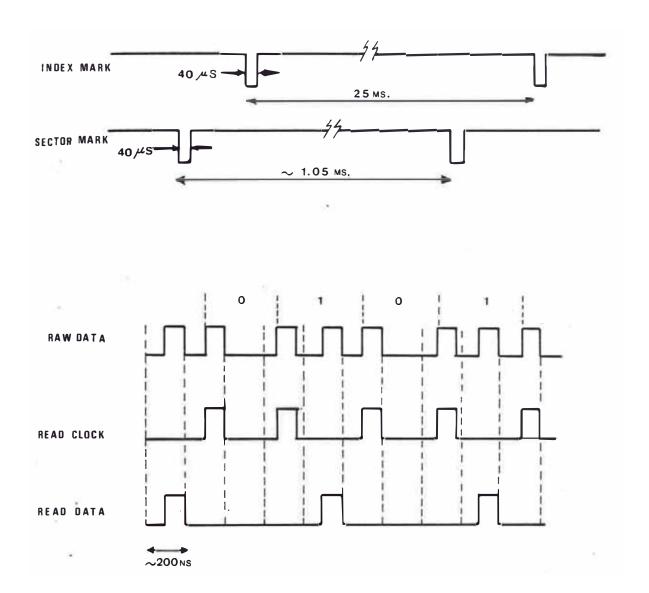

Como sabemos toda información es grabada en el disco conjuntamente con la señal de sincronismo, esto permite una fácil recuperación de la data grabada. La figura N° 3.1 ilustra la forma de la señal que se aplica a las cabezas de escritura/lectura del disco, el bit de data va insertado entre dos pulsos de clock, en el caso de que el bit de dato sea un cero lógico no habrá pulso entre los dos pulsos de clock, si la información a grabar fuera un tren de unos lógicos la señal sería una onda de doble frecuencia que en el caso de que se grabara un tren de ceros lógicos, ésta es la razón de que a esta técnica de grabación se le denomine Técnica de Frecuencia Doble.

El tiempo de acceso se refiere al tiempo que interviene el mecanismo de movimiento de las cabezas de escritura y lectura en posicionar a éstas sobre un track de terminado. La Unidad de Disco posee dos conectores de

interface, uno de éllos llamado el conector de entrada y recibe información de un controlador o de otra Unidad de Disco, el otro conector llamado conector de salida pro - vee la conexión con una siguiente unidad de disco, es decir, varias unidades de disco pueden ser conectadas en cadena y controladas a la vez por un solo CPU. En caso de que solamente se use una Unidad de Disco, este conec - tor de salida debe llevar el cable adaptador de impedancia correspondiente, caso contrario se pueden presentar problemas al momento de grabar o recuperar información.

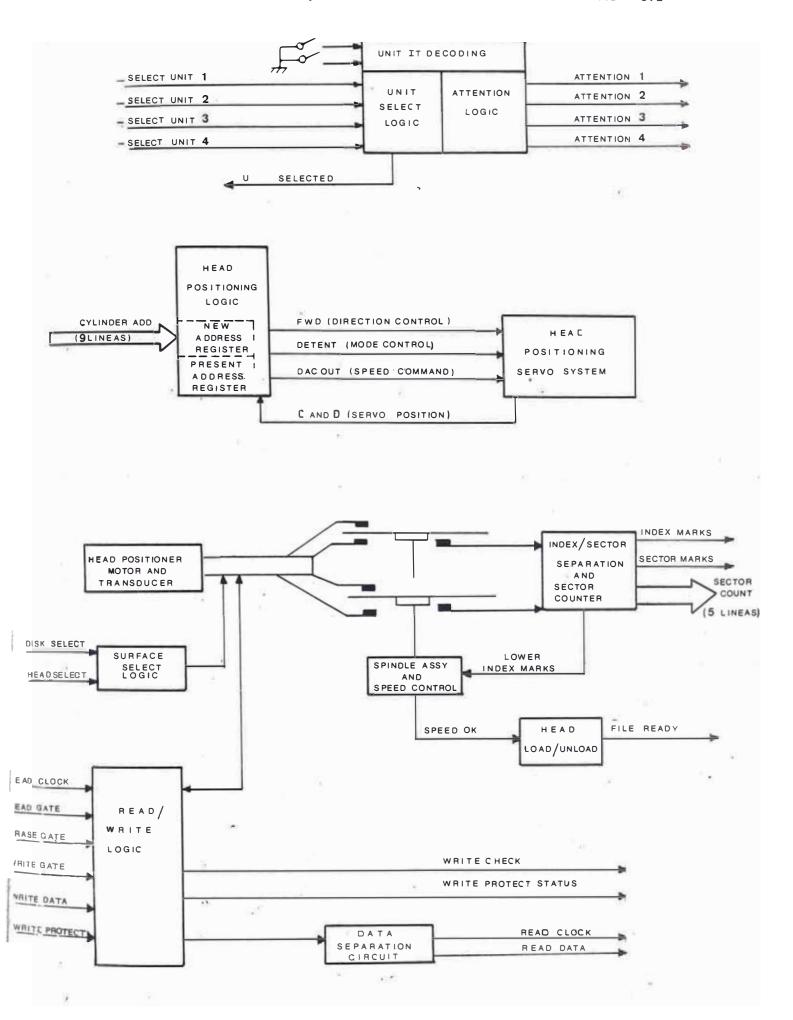

En el diagrama N° 3.2 observamos el diagrama de bloques de la unidad de disco. El bloque denominado: UNIT ID Decoding es el encargado de seleccionar a la Unidad, esta solo responde a una de las cuatro líneas de selección (4 posibles unidades de disco que pueden ser conectadas en cadena). La dirección de la unidad se establece mediante un par de switches.

El bloque denominado: Head Positioning Logic posi - ciona la cabeza de lectura/escritura en la dirección es-pecificada por el Controlador (en este caso por la Unidad de Control) enviando señales al bloque Head Positioning Servo System.

El bloque de lógica de lectura/escritura recibe señales del controlador como las que se muestran y efectúa la lectura y grabación en el disco. Durante lectura recibe los bits de datos mezclados con los bits de clock,

por lo cual hay un bloque llamado Circuito Separador de Datos, el cual a su salida provee a través de dos líneas independientes los bits de datos y los bits de clock.

Como se sabe el Disco Magnético se encuentra formado por varios sectores (en este caso son 24 sectores) un Index, el cual sirve como punto de referencia para la identificación de los sectores (ver información básica sobre los discos magnéticos en el Apéndice). Tanto sectores como el Index se encuentran físicamente repre sentados a través de ranuras en el disco giratorio sobre el cual está el disco magnético. Estas ranuras son de tectadas a través de sensores ópticos proveyendo pulsos que van aalimentar a un contador de sectores (5 bits para los 24 sectores que se disponen). El pulso de Index no debe alimentar a este contador sino mas bien resetear lo, ya que el Index es una referencia de donde empieza el sector N°1. Para ésto, se dispone de una lógica que separa el pulso de Index de los restantes pulsos de sector.

El Bloque Spindle Assy. and Speed Control comprende el motor que hace girar el disco a una velocidad constan te y la lógica que controla la velocidad de este motor.

Esta detección de velocidad se efectúa en base al pulso del Index. Cuando la velocidad no es la que debe ser las cabezas de escritura/lectura se encuentran des - cargadas, es decir, no se actúa el mecanismo que mantie-

la superficie de las cabezas muy cerca a la superficie - del disco.

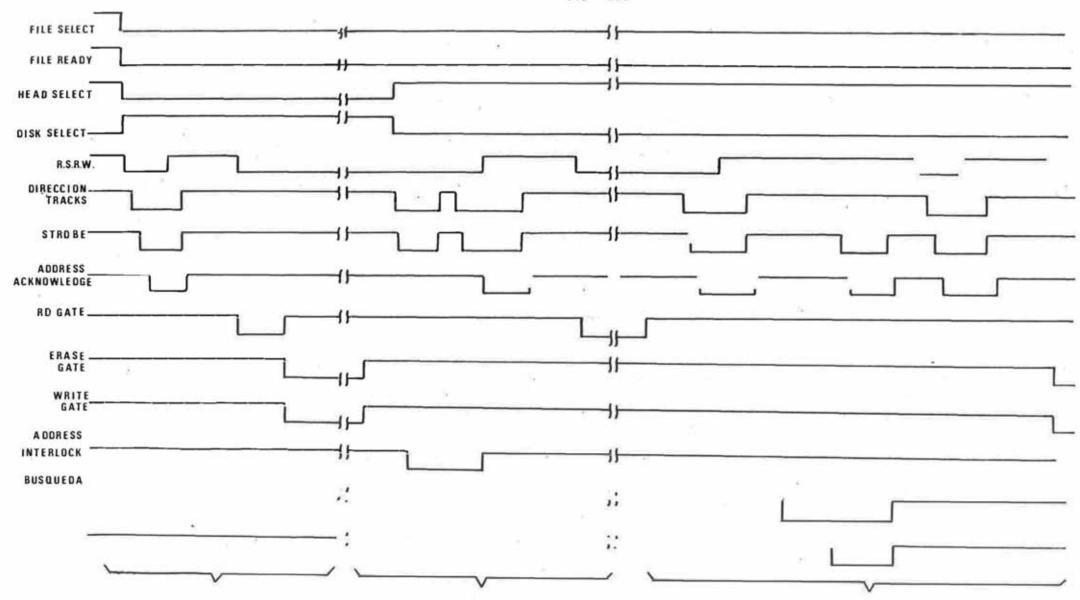

### 3.2 Señales de Control de la Unidad de Disco Diablo

Todas las señales necesarias para controlar la Unidad de Disco se encuentran disponibles en el Conector de

Interface, es importante conocer la función de cada una

de estas señales para poder comprender el diseño de la

Interface de Disco.

A continuación se describe brevemente la función de cada pin del conector de Interface:

#### Lineas de entrada

SELECT LINES; son cuatro líneas y sirven para seleccio - nar la unidad cuando se trabaja con varias unidades co- nectadas en una configuración de cadena. Cada unidad po see 2 switches, los cuales sirven para identificar a la unidad 1, 2, 3 ó 4. Cuando esta señal no está activa to das las demás señales de la interface permanecen deshabi litadas excepto la señal ATTENTION.

DISK SELECT; selecciona el disco, un cero lógico selec - ciona el disco removible y un uno lógico selecciona el disco fijo.

HEAD SELECT; esta línea selecciona a la cabeza superior o inferior. Un cero lógico selecciona la cabeza superior, un uno lógico selecciona la cabeza inferior.

CYLINDER ADDRESS: está formado por 9 bits e indica la di rección del cilindro en binario absoluto.

STROBE; es usado para habilitar la dirección del cilin - dro, debe estar activa hasta que la unidad de disco responde con la señal -ADDRESS ACKNOWLEDGE informando que ha reconocido la dirección de cilindro especificada.

RESTORE; esta linea sirve para posicionar las cabezas so bre el Track Cero a la vez que resetea el registro de dirección de Track.

WRITE GATE; estando en cero lógico esta señal provee corriente de escritura a la cabeza seleccionada. Esta señal debe estar activa durante la escritura de todo un

sector.

ERASE GATE: estando en un nivel bajo provee corriente de borrado a la cabeza seleccionada.

WRITE DATA & CLOCK; esta línea envía a la unidad de disco la data multiplexada con el clock, cada pulso va a representar un cambio de flujo magnético a grabarse en la superficie del disco; el ancho de los pulsos debe estar en el rango de 100 á 150 ns.

READ GATE; estando en cero lógico habilita las señales de Read Clock y Read Data que provienen de la Unidad de Disco.

Señales de Salida:

FILE READY; permanece en nivel bajo siempre y cuando se cumplan las siguientes condiciones:

- Hay alimentación al sistema

- Disco removible cargado

- Switch en la posición RUN

- Ciclo de encendido completado

- Señal -WRITE CHECK en nivel alto

- Señal -UNIT SELECTED en nivel bajo

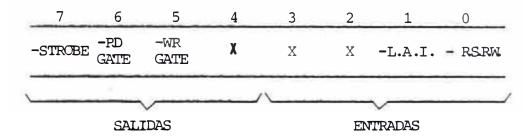

#### READY TO SEEK, READ OR WRITE (RSRW)

Esta señal permanece en un nivel bajo cuando el disco se encuentra en la condición de FILE READY y además no está efectuando ninguna operación de búsqueda. Cuando la uni dad recibe un comando válido de búsqueda esta línea se va a un nivel alto inmediatamente después de recibir un STROBE y retorna al nivel bajo cuando las cabezas se encuentran posicionadas sobre la nueva dirección.

#### ADDRESS ACKNOWLEDGE (ADRS ACK)

Un nivel bajo en esta línea indica que ha sido aceptada una dirección en una instrucción de búsqueda. Si la bús queda se especifica a los tracks mayores de 407 esta señal permanecerá inactiva ya que estas direcciones no son válidas.

LOGICAL ADDRESS INTERLOCK: (LAI) Estando en un nivel ba jo indica que se ha recibido una dirección mayor de 407 y que la instrucción de búsqueda no puede ser efectuada. Esta señal se resetea con la siguiente señal de -ADRSACK o con un comando de Restore.

SEEK INCOMPLETE; un nivel bajo indica que algún desperfecto ha causado que no se complete la operación de búsqueda, este nivel se mantendrá hasta que se reciba un

comando de RESTORE y un STROBE o hasta que el switch de

la unidad es colocado en la posición de LOAD.

INDEX MARK; esta línea provee un pulso negativo de 40 mi cro segundos por cada revolución del disco, indicando el inicio del sector cero, para esto la parte inferior del plato giratorio que mueve el disco presenta unas ranuras, las cuales son detectadas por un sensor óptico.

READ CLOCK; en una unidad seleccionada, esta señal provee los pulsos de clock, los cuales han sido separados de la señal de data durante una operación de lectura. El an cho del pulso es nominalmente 100 + 50 nsec.

WRITE PROTECT STATUS; un nivel bajo indica que no se pue de escribir sobre el disco. El operador puede anular es te estado presionando el switch PROTECT en el panel fron tal, permitiendo así la escritura en el disco.

SECTOR MARK; esta línea provee un pulso negativo de 40 microsegundos por cada ranura en el plato giratorio, es decir, por cada sector.

SECTOR ADDRESS; esta palabra de 5 bits indican el sector sobre el cual se encuentran en ese momento las cabezas; esta señal es derivada de unos contadores cuyo clock es la señal SECTOR MARK y se resetean con el primer sector mark después del INDEX MARK.

Estas son las principales señales del disco Diablo 44B, existen algunas pocas más pero no serán usadas en el diseño de la interface.

En la figura N° 3.3 podemos observar el diagrama de tiempo del funcionamiento del disco, las operaciones de búsqueda, de escritura y lectura.

Para hacer efectiva la grabación y posterior lectura de los datos es necesario delimitar en el disco áreas definidas, las cuales contengan información pre-establecida y faciliten la interacción de la unidad central con el disco. Esto se logra con el proceso de formateo. For matear es la acción de grabar en el disco la identificación de cada sector, así como delimitar las diferentes partes que conforman un sector. Todo disco antes de ser usado debe ser formateado. En el formateo también se graban zonas de Guarda, las cuales aseguran un número constante de bits de información en cada sector a pesar de variaciones en la velocidad del disco, variación del espaciado entre sectores, alineamiento del transductor del Index, etc.

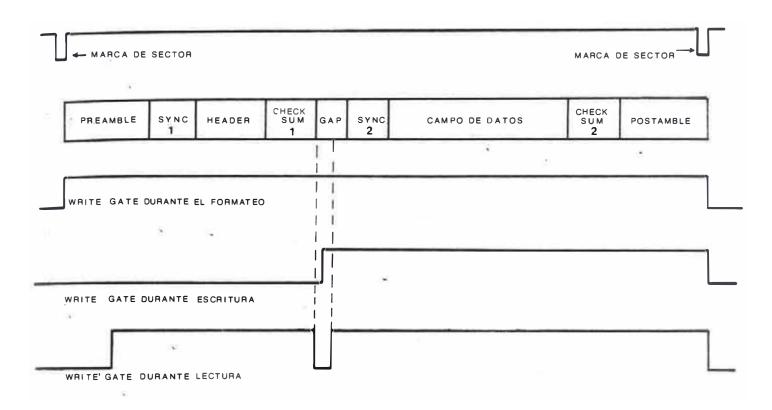

El formato de cada sector se muestra en la figura  $N^{\circ}$  3.4.

PREAMBLE; es una zona de guarda que asegura contra las - variaciones del transductor del Index, alineamiento del disco removible y tiempo de recuperación del amplifica - dor de lectura. El Preamble es generalmente llenado de caracteres hexadecimales 00.

# DIAGRAMA DE TIEMPO DE LA UNIDAD DE DISCO

FIG 3.3

# FORMATO DE UN SECTOR DEL DISCO Y DIAGRAMAS DE TIEMPO

FIG 3.4

SINC 1; es un byte de sincronismo, generalmente está for mado por 2 caracteres hexadecimales 03. Es necesario para indicar el final de la zona de Preamble y el inicio del Header.

HEADER; este campo generalmente es llenado con la dirección del cilindro, cabeza y sector sobre los cuales se encuentra la cabeza de R/W.

HEADER CHECK SUM (Check Sum I); es un caracter de chequeo originado por la unidad central durante el proceso de escritura. Este caracter es comparado con el caracter hallado al hacer la lectura para asegurar que el Header ha sido leído correctamente.

GAP; este es un campo opcional y es usado como un Preamble para el campo de data. Es usado en los sistemas en los cuales el Header no es vuelto a escribir durante la escritura de data. Es escrito durante el formateo.

SYNC 2; se usa para indicar el final del GAP y el inicio de la Data.

DATA FIELD; información a ser grabada o leída.

DATA CHECK SUM (Check Sum 2); se origina durante la estecritura, este caracter es comparado con el caracter obte nido al hacer la lectura para asegurar que el campo de data fue leído correctamente.

POSTAMBLE; son todos los pulsos de clock grabados hasta la detección del siguiente sector. Esta zona contrarres ta las variaciones en la rotación del disco, variaciones en el clock de escritura.

#### 3.3 Operaciones típicas con la unidad de disco Diablo

A continuación se detalla los pasos a seguir durante las operaciones Formateo, Escritura de Data y Lectura

### Operación de Escritura de Formato (Formateo)

- 1.- Detectar Sector Zero

- 2.- Habilitar puerta de Escritura/Borrado

- 3.- Escribir Preamble (ceros)

- 4.- Escribir Sync 1, (03 hex)

- 5.- Escribir Header y Check Sum 1

- 6.- Escribir Gap (ceros)

- 7.- Escribir Sincronismo 2, Campo de Data y Check Sum 2.

Durante la operación de formateo generalmente se es

cribe en el campo de Data ceros o la misma informa

ción del Header/Check Sum 1. Sincronismo 2 general

mente es 03.

- 8.- Escribir Postamble (ceros) hasta que se detecte el inicio del siguiente sector.

- 9.- Durante el formateo la compuerta de Escritura/Lectura ra no debe ser deshabilitada hasta que se acabe de formatear el último sector del Track. Todos los sectores del track siguen el mismo procedimiento y lo único que varía es el Header y el Check Sum 1. Este mismo track debe ser leído en la siguiente revolución para verificar si ha sido correcto el formateo.

#### Operación de Escritura de Data

- 1.- Detectar el inicio del Sector a escribir

- 2.- Habilitar la compuerta de Lectura luego de un retardo igual a la mitad del Preamble.

- 3.- Leer los ceros de la zona de Preamble hasta detec tar Sincronismo 1.

- 4.- Leer Sincronismo 1 y Header/Check Sum 1 para verifi car que se está leyendo el sector correcto.

- 5.- Deshabilitar Compuerta de Lectura después del último bit de Check Sum 1.

- 6.- Habilitar la compuerta de escritura luego de un tiem po equivalente a un byte (8 bits).

- 7.- Escribir el Gap (ceros).

- 8.- Fscribir Sincronismo 2.

- 9.- Escribir Campo de Data y Check Sum 2.

- 10.- Deshabilitar la compuerta de escritura al detectar el inicio del siguiente sector.

# Operación de Lectura

- 1.- Detectar el inicio del Sector deseado.

- 2.- Habilitar la compuerta de lectura luego de un retar do equivalente a la mitad del Preamble.

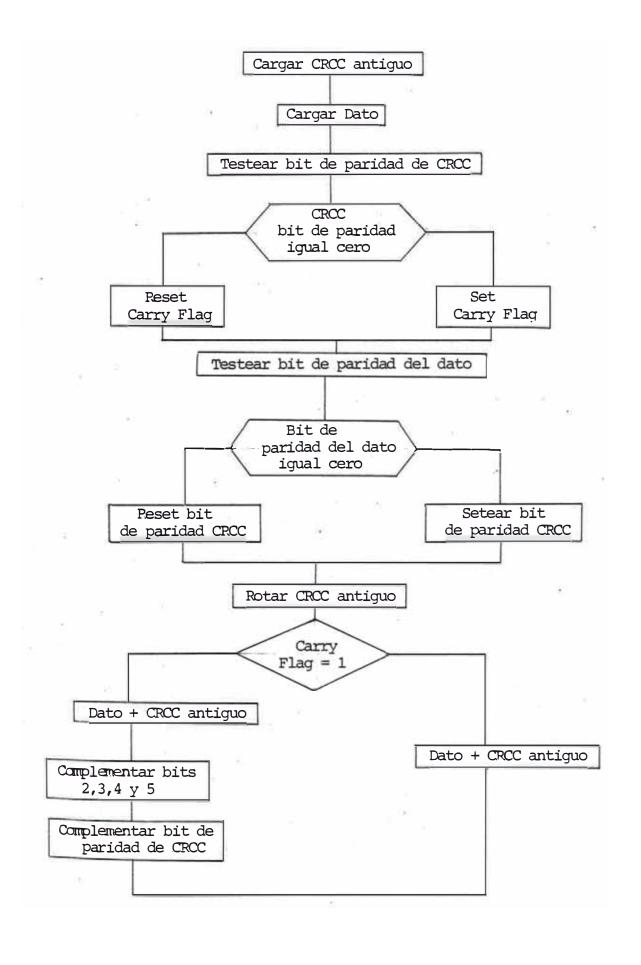

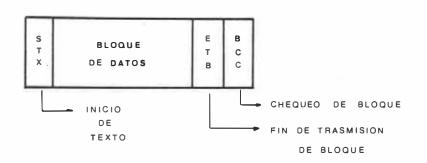

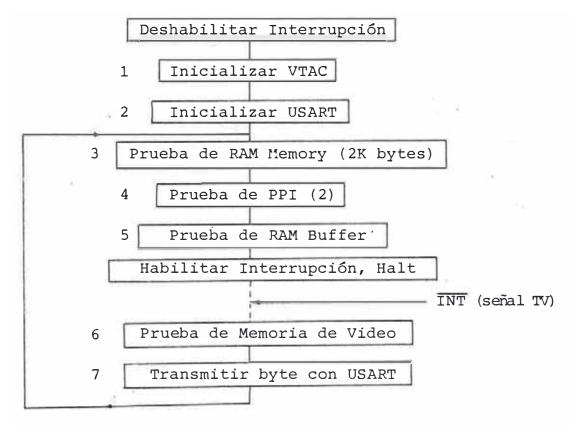

- 3.- Leer los ceros de la zona de Preamble hasta detec tar el caracter 03 Hex el cual es el caracter de sincronismo.